Right side

- Line deflection output UNIT + SMPS Pulse Command/POWER drive + Supply Trafo + EHT

Center

- Synch + Frame deflection + Drive UNIT

Left

- Signal Processing / Video Luminance + Chrominance + RGB Amplifier

- Tuner

- IF Video + Sound

- Sound amplifier Unit

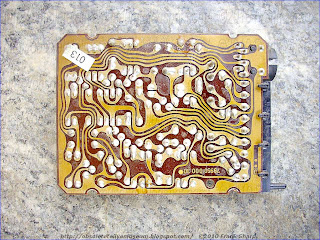

LINE/HORIZONTAL DEFLECTION UNIT (HORIZONTAL- MODUL Best.Nr. 7807021000)

SMPS - BU208A (TELEFUNKEN)

LINE DEFLECTION OUTPUT- BU208A (TELEFUNKEN)

NOTE THAT THE EHT TRAFO HAS FUNCTION EVEN AS LINE SYNCHRONIZED SUPPLY SMPS TRAFO.

NOTE THAT THE EHT TRAFO HAS FUNCTION EVEN AS LINE SYNCHRONIZED SUPPLY SMPS TRAFO.BU208(A)

Silicon NPNnpn transistors,pnp transistors,transistors

Category: NPN Transistor, Transistor

MHz: <1 MHz

Amps: 5A

Volts: 1500V

HIGH VOLTAGE CAPABILITY

JEDEC TO-3 METAL CASE.

DESCRIPTION

The BU208A, BU508A and BU508AFI are

manufactured using Multiepitaxial Mesa

technology for cost-effective high performance

and use a Hollow Emitter structure to enhance

switching speeds.

APPLICATIONS:

* HORIZONTAL DEFLECTION FOR COLOUR TV With 110° or even 90° degree of deflection angle.

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

VCES Collector-Emit ter Voltage (VBE = 0) 1500 V

VCEO Collector-Emit ter Voltage (IB = 0) 700 V

VEBO Emitter-Base Voltage (IC = 0) 10 V

IC Collector Current 8 A

ICM Collector Peak Current (tp < 5 ms) 15 A

TO - 3 TO - 218 ISOWATT218

Ptot Total Dissipation at Tc = 25 oC 150 125 50 W

Tstg Storage Temperature -65 to 175 -65 to 150 -65 to 150 oC

Tj Max. Operating Junction Temperature 175 150 150 °C

SABA ULTRACOLOR T56Q75 QUARTZ COMPUTER CHASSIS Q110 CIRCUIT ARRANGEMENT IN A PICTURE DISPLAY DEVICE UTILIZING A STABILIZED SUPPLY VOLTAGE CIRCUIT:

Line synch Switched Mode Power Supply with Line deflection output Transistor Drive Circuit:

A stabilized supply voltage circuit for a picture display device comprising a chopper wherein the switching signal has the line frequency and is duration-modulated. The coil of the chopper constitutes the primary winding of a transformer a secondary winding of which drives the line output transistor so that the switching transistor of the chopper also functions as a driver for the line output stage. The oscillator generating the switching signal may be the line oscillator. In a special embodiment the driver and line output transistor conduct simultaneously and in order to limit the base current of the line output transistor a coil shunted by a diode is incorporated in the drive line of the line output transistor. Other secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode of the chopper so as to generate further stabilized supply voltages.

between said driving means and said second transistor and a third diode shunt coupled to said coil and being poled to conduct when said 6. A circuit as claimed in claim 1 further comprising a horizontal oscillator coupled to said first transistor, said oscillator being the 7. A circuit as claimed in claim 1 further comprising means coupled to said inductor for deriving filament voltage for said display device.

Description:

Such a circuit arrangement is known from German "Auslegeschrift" 1.293.304. wherein a circuit arrangement is described which has for its object to convert an input direct voltage which is generated between two terminals into a different direct voltage. The circuit employs a switch connected to the first terminal of the input voltage and periodically opens and closes so that the input voltage is converted into a pulsatory voltage. This pulsatory voltage is then applied to a coil. A diode is arranged between the junction of the switch and the coil and the second terminal of the input voltage whilst a load and a charge capacitor in parallel thereto are arranged between the other end of the coil and the second terminal of the input voltage. The assembly operates in accordance with the known efficiency principle i.e., the current supplied to the load flows alternately through the switch and through the diode. The function of the switch is performed by a switching transistor which is driven by a periodical pulsatory voltage which saturates this transistor for a given part of the period. Such a configuration is known under different names in the literature; it will be referred to herein as a "chopper."

A known advantage thereof, is that the switching transistor must be able to stand a high voltage or provide a great current but it need not dissipate a great power. The output voltage of the chopper is compared with a constant reference voltage. If the output voltage attempts to vary because the input voltage and/or the load varies, a voltage causing a duration modulation of the pulses is produced at the output of the comparison arrangement. As a result the quantity of the energy stored in the coil varies and the output voltage is maintained constant. In the German "Auslegeschrift" referred to it is therefore an object to provide a stabilized supply voltage device.

In the circuit arrangement according to the mentioned German "Auslegeschrift" the frequency of the load variations or a harmonic thereof is chosen as the frequency for the switching voltage. Particularly when the load fed by the chopper is the line deflection circuit of a picture display device, wherein thus the impedance of the load varies in the rhythm of the line frequency, the frequency of the switching voltage is equal to or is a multiple of the line frequency.

It is to be noted that the chopper need not necessarily be formed as that in the mentioned German "Auslegeschrift." In fact, it is known from literature that the efficiency diode and the coil may be exchanged. It is alternatively possible for the coil to be provided at the first terminal of the input voltage whilst the switching transistor is arranged between the other end and the second terminal of the input voltage. The efficiency diode is then provided between the junction of said end and the switching transistor and the load. It may be recognized that for all these modifications a voltage is present across the connections of the coil which voltage has the same frequency and the same shape as the pulsatory switching voltage. The control voltage of a line deflection circuit is a pulsatory voltage which causes the line output transistor to be saturates and cut off alternately. The invention is based on the recognition that the voltage present across the connections of the coil is suitable to function as such a control voltage and that the coil constitutes the primary of a transformer. To this end the circuit arrangement according to the invention is characterized in that a secondary winding of the transformer drives the switching element which applies a line deflection current to line deflection coils and by which the voltage for the final anode of a picture display tube which forms part of the picture display device is generated, and that the ratio between the period during which the switching transistor is saturated and the entire period, i.e., the switching transistor duty cycle is between 0.3 and 0.7 during normal operation.

The invention is also based on the recognition that the duration modulation which is necessary to stabilize the supply voltage with the switching transistor does not exert influence on the driving of the line output transistor. This resides in the fact that in case of a longer or shorter cut-off period of the line output transistor the current flowing through the line deflection coils thereof is not influenced because of the efficiency diode current and transistor current are taken over or, in case of a special kind of transistor, the collector-emitter current is taken over by the base collector current and conversely. However, in that case the above-mentioned ratios of 0.3 : 0.7 should be taken into account since otherwise this take-over principle is jeopardized.

As will be further explained the use of the switching transistor as a driver for the line output transistor in an embodiment to be especially described hereinafter has the further advantage that the line output transistor automatically becomes non-conductive when this switching transistor is short circuited so that the deflection and the EHT for the display tube drop out and thus avoid damage thereof.

As will be further explained the use of the switching transistor as a driver for the line output transistor in an embodiment to be especially described hereinafter has the further advantage that the line output transistor automatically becomes non-conductive when this switching transistor is short circuited so that the deflection and the EHT for the display tube drop out and thus avoid damage thereof.Due to the step according to the invention the switching transistor in the stabilized supply functions as a driver for the line deflection circuit. The circuit arrangement according to the invention may in addition be equipped with a very efficient safety circuit so that the reliability is considerably enhanced, which is described in the U.S. Pat. No. 3,629,686. The invention is

furthermore based on the recognition of the fact that the pulsatory voltage present across the connections of the coil is furthermore used and to this end the circuit arrangement according to the invention is characterized in that secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode so as to generate further stabilized direct voltages, one end of said diodes being connected to ground.

furthermore based on the recognition of the fact that the pulsatory voltage present across the connections of the coil is furthermore used and to this end the circuit arrangement according to the invention is characterized in that secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode so as to generate further stabilized direct voltages, one end of said diodes being connected to ground.In order that the invention may be readily carried into effect, a few embodiments thereof will now be described in detail by way of example with reference to the accompanying diagrammatic drawings in which:

FIG. 1 shows a principle circuit diagram wherein the chopper and the line deflection circuit are further shown but other circuits are not further shown.

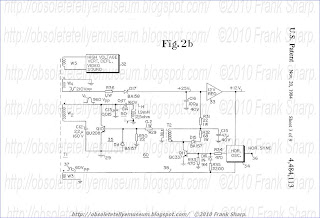

FIGS. 2a, 2b and 2c show the variation as a function of time of two currents and of a voltage occurring in the circuit arrangement according to FIG. 1.

FIGS. 3a 3b, 3c and 3d show other embodiments of the chopper.

FIGS. 4a and 4b show modifications of part of the circuit arrangement of FIG. 1.

In FIG. 1 the reference numeral 1 denotes a rectifier circuit which converts the mains voltage supplied thereto into a non-stabilized direct voltage. The collector of a switching transistor 2 is connected to one of the two terminals between which this direct voltage is obtained, said transistor being of the npn-type in this embodiment and the base of which receives a pulsatory voltage which originates through a control stage 4 from a modulator 5 and causes transistor 2 to be saturated and cut off alternately. The voltage waveform 3 is produced at the emitter of transistor 2. In order to maintain the output voltage of the circuit arrangement constant, the duration of the pulses provided is varied in modulator 5. A pulse oscillator 6 supplies the pulsatory voltage to modulator 5 and is synchronized by a signal of line frequency which originates from the line oscillator 6' present in the picture display device. This line oscillator 6' is in turn directly synchronized in known manner by pulses 7' of line frequency which are present in the device and originate for example from a received television signal if the picture display device is a television receiver. Pulse oscillator 6 thus generates a pulsatory voltage the repetition frequency of which is the line frequency.

In FIG. 1 the reference numeral 1 denotes a rectifier circuit which converts the mains voltage supplied thereto into a non-stabilized direct voltage. The collector of a switching transistor 2 is connected to one of the two terminals between which this direct voltage is obtained, said transistor being of the npn-type in this embodiment and the base of which receives a pulsatory voltage which originates through a control stage 4 from a modulator 5 and causes transistor 2 to be saturated and cut off alternately. The voltage waveform 3 is produced at the emitter of transistor 2. In order to maintain the output voltage of the circuit arrangement constant, the duration of the pulses provided is varied in modulator 5. A pulse oscillator 6 supplies the pulsatory voltage to modulator 5 and is synchronized by a signal of line frequency which originates from the line oscillator 6' present in the picture display device. This line oscillator 6' is in turn directly synchronized in known manner by pulses 7' of line frequency which are present in the device and originate for example from a received television signal if the picture display device is a television receiver. Pulse oscillator 6 thus generates a pulsatory voltage the repetition frequency of which is the line frequency.The emitter of switching transistor 2 is connected at one end to the cathode of an efficiency diode 7 whose other end is connected to the second input voltage terminal and at the other end to primary winding 8 of a transformer 9. Pulsatory voltage 3 which is produced at the cathode of efficiency diode 7 is clamped against the potential of said second terminal during the intervals when this diode conducts. During the other intervals the pulsatory voltage 3 assumes the value V i . A charge capacitor 10 and a load 11 are arranged between the other end of winding 8 and the second input voltage terminal. The elements 2,7,8,10 and 11 constitute a so-called chopper producing a direct voltage across charge capacitor 10, provided that capacitor 10 has a sufficiently great value for the line frequency and the current applied to load 11 flowing alternately through switching transistor 2 or through efficiency diode 7. The output voltage V o which is the direct voltage produced across charge capacitor 10 is applied to a comparison circuit 12 which compares the voltage V o with a reference voltage. Comparison circuit 12 generates a direct voltage which is applied to modulator 5 so that the duration of the effective period δ T of switching transistor 2 relative to the period T of pulses 3 varies as a function of the variations of output voltage V 0 . In fact, it is readily evident that output voltage V o is proportional to the ratio δ :

V o = V i . δ

Load 11 of the chopper consists in the consumption of parts of the picture display device which are fed by output voltage V 0 . In a practical embodiment of the circuit arrangement according to FIG. 1 wherein the mains alternating voltage has a nominal effective value of 220 V and the rectified voltage V i is approximately 270 V, output voltage V o for δ = 0.5 is approximately 135 V. This makes it also possible, for example, to feed a line deflection circuit as is shown in FIG. 1 wherein load 11 then represents different parts which are fed by the chopper. Since voltage V o is maintained constant due to pulse duration modulation, the supply voltage of this line deflection circuit remains constant with the favorable result that the line amplitude(= the width of the picture displayed on the screen of the picture display tube) likewise remains constant as well as the EHT required for the final anode of the picture display tube in the same circuit arrangement independent of the variations in the mains voltage and the load on the EHT generator (= variations in brightness).

However, variations in the line amplitude and the EHT may occur as a result of an insufficiently small internal impedance of the EHT generator. Compensation means are known for this purpose. A possibility within the scope of the present invention is to use comparison circuit 12 for this purpose. In fact, if the beam current passes through an element having a substantially quadratic characteristic, for example, a voltage-dependent resistor, then a variation for voltage V o may be obtained through comparison circuit 12 which variation is proportional to the root of the variation in the EHT which is a known condition for the line amplitude to remain constant.

However, variations in the line amplitude and the EHT may occur as a result of an insufficiently small internal impedance of the EHT generator. Compensation means are known for this purpose. A possibility within the scope of the present invention is to use comparison circuit 12 for this purpose. In fact, if the beam current passes through an element having a substantially quadratic characteristic, for example, a voltage-dependent resistor, then a variation for voltage V o may be obtained through comparison circuit 12 which variation is proportional to the root of the variation in the EHT which is a known condition for the line amplitude to remain constant.In addition this facilitates smoothing of voltage V o since the repetition frequency of pulsatory voltage 3 is many times higher than that of the mains and a comparatively small value may be sufficient for charge capacitor 10. If charge capacitor 10 has a sufficiently high value for the line frequency, voltage V o is indeed a direct voltage so that a voltage having the same form as pulsatory voltage 3 is produced across the terminals of primary winding 8. Thus voltages which have the same shape as pulsatory voltage 3 but have a greater or smaller amplitude are produced across secondary windings 13, 14 of transformer 9 (FIG. 1 shows only 2 secondary windings but there may be more). The invention is based on the recognition that one end of each secondary winding is connected to earth while the other end thereof drives a diode, the winding sense of each winding and the direction of conductance of each diode being chosen to be such that these diodes conduct during the same period as does efficiency diode 7. After smoothing, stabilized supply voltages, for example, at terminal 15 are generated in this manner at the amplitudes and polarities required for the circuit arrangements present in the picture display device. In FIG. 1 the voltage generated at terminal 15 is, for example, positive relative to earth. It is to be noted that the load currents of the supply voltages obtained in this manner cause a reduction of the switching power which is economized by efficiency diode 7. The sum of all diode currents including that of diode 7 is in fact equal to the current which would flow through diode 7 if no secondary winding were wound on transformer 9 and if no simultaneous diode were used. This reduction may be considered an additional advantage of the circuit arrangement according to the invention, for a diode suitable for smaller powers may then be used. However, it will be evident that the overall secondary load must not exceed the primary load since otherwise there is the risk of efficiency diode 7 being blocked so that stabilization of the secondary supply voltages would be out of the question.

It is to be noted that a parabola voltage of line frequency as shown at 28 is produced across the charge capacitor 10 if this capacitor is given a smaller capacitance so that consequently the so-called S-correction is established.

In FIG. 1 charge capacitors are arranged between terminals 15 etc. and earth so as to ensure that the voltages on these points are stabilized direct voltages. If in addition the mean value of the voltage on one of these terminals has been made equal to the effective value of the alternating voltage which is required for heating the filament of the picture display tube present in the picture display device, this voltage is suitable for this heating. This is a further advantage of the invention since the cheap generation of a stabilized filament voltage for the picture display tube has always been a difficult problem in transistorized arrangements.

A further advantage of the picture display device according to the invention is that transformer 9 can function as a separation transformer so that the different secondary windings can be separated from the mains and their lower ends can be connected to ground of the picture display device. The latter step makes it possible to connect a different apparatus such as, for example, a magnetic recording and/or playback apparatus to the picture display device without earth connection problems occurring.

In FIG. 1 the reference numeral 14 denotes a secondary winding of transformer 9 which in accordance with the previously mentioned recognition of the invention can drive line output transistor 16 of the line deflection circuit 17. Line deflection circuit 17 which is shown in a simplified form in FIG. 1 i

ncludes inter alia line deflection coils 18 and an EHT transformer 19 a secondary winding 20 of which serves for generating the EHT required for the acceleration anode of the picture display tube. Line deflection circuit 17 is fed by the output voltage V o of the chopper which voltage is stabilized due to the pulse duration modulation with all previously mentioned advantages. Line deflection circuit 17 corresponds, for example, to similar arrangements which have been described in U.S. Pat. No. 3,504,224 issued Mar. 31, 1970 to J.J. Reichgelt et al., U.S. patent application Ser. No. 737,009 filed June 14, 1968 by W. H. Hetterscheid and U.S. application Ser. No. 26,497 filed April 8, 1970 by W. Hetterscheid et al. It will be evident that differently formed lined deflection circuits are alternatively possible.

It will now be shown that secondary winding 14 can indeed drive a line deflection circuit so that switching transistor 2 can function as a driver for the line deflection. FIGS. 2a and b show the variation as a function of time of the current i C which flows in the collector of transistor 16 and of the drive voltage v 14 across the terminals of secondary winding 14. During the flyback period (0, t 1 ) transistor 16 must be fully cut off because a high voltage peak is then produced at its collector; voltage v 14 must then be absolutely negative. During the scan period (t 1 , t 4 ) a sawtooth current i C flows through the collector electrode of transistor 16 which current is first negative and then changes its direction. As the circuit arrangement is not free from loss, the instant t 3 when current i C becomes zero lies, as is known, before the middle of the scan period. At the end t 4 of the scan period transistor 16 must be switched off again. However, since transistor 16 is saturated during the scan period and since this transistor must be suitable for high voltages and great powers so that its collector layer is thick, this transistor has a very great excess of charge carriers in both its base and collector layers. The removal of these charge carriers takes a period t s which is not negligible whereafter the transistor is indeed switched off. Thus the fraction δ T of the line period T at which v 14 is positive must end at the latest at the instant (t 4 - t s ) located after the commencement (t = 0) of the previous flyback.

The time δ T may be initiate

d at any instant t 2 which is located between the end t 1 of the flyback period and the instant t 3 when collector current i C reverses its direction. It is true that emitter current flows through transistor 16 at the instant t 2 , but collector current i C is not influenced thereby, at least not when the supply voltage (= V o ) for line deflection circuit 17 is high enough. All this has been described in the U.S. Pat. No. 3,504,224. The same applies to line deflection circuits wherein the collector base diode does not function as an efficiency diode as is the case in the described circuit 17, but wherein an efficiency diode is arranged between collector and emitter of the line output transistor. In such a case the negative part of the current i C of FIG. 2a represents the current flowing through the said efficiency diode.

d at any instant t 2 which is located between the end t 1 of the flyback period and the instant t 3 when collector current i C reverses its direction. It is true that emitter current flows through transistor 16 at the instant t 2 , but collector current i C is not influenced thereby, at least not when the supply voltage (= V o ) for line deflection circuit 17 is high enough. All this has been described in the U.S. Pat. No. 3,504,224. The same applies to line deflection circuits wherein the collector base diode does not function as an efficiency diode as is the case in the described circuit 17, but wherein an efficiency diode is arranged between collector and emitter of the line output transistor. In such a case the negative part of the current i C of FIG. 2a represents the current flowing through the said efficiency diode.After the instant t 3 voltage v 14 must be positive. In other words, the minimum duration of the period T when voltage v 14 must be positive is (t 4 - t s ) - t 3 whilst the maximum duration thereof is (t 4 - t s ) - t 1 . In a television system employing 625 lines per raster the line period t 4 is approximately 64 μus and the flyback period is approximately 12 μus. Without losses in the circuit arrangement instant t 3 would be located approximately 26 μus after the instant t 1 , and with losses a reasonable value is 22 μus which is 34 μus after the commencement of the period. If for safety's sake it is assumed that t s lasts approximately 10 μus, the extreme values of δ T are approximately 20 and 42 μus and consequently the values for δ are approximately 0.31 and 0.66 at a mean value which is equal to approximately 0.49. It was previously stated that a mean value of δ = 0.5 was suitable. Line deflection circuit 17 can therefore indeed be used in combination with the chopper in the manner described, and the relative variation of δ may be (0.66 - 0.31) : 0.49 = 71.5 percent. This is more than necessary to obviate the variations in the mains voltage or in the various loads and to establish the East-West modulation and ripple compensation to be described hereinafter. In fact, if it is assumed that the mains voltage varies between -15 and +10 percent of the nominal value of 220 V, while the 50 Hz ripple voltage which is superimposed on the input voltage V i has a peak-to-peak value of 40 V and V i is nominally 270 V, then the lowest occurring V i is:

0.85 × 270 V - 20 V = 210 V and the highest occurring V i is

1.1 × 270 V + 20 V = 320 V. For an output voltage V o of 135 V the ratio must thus vary between

δ = 135 : 210 = 0.64 and δ = 135 : 320 = 0.42.

A considerable problem presenting itself is that of the simultaneous or non-simultaneous drive of line output transistor 16 with switching transistor 2, it being understood that in case of simultaneous drive both trans

stors are simultaneously bottomed, that is during the period δ T. This depends on the winding sense of secondary winding 14 relative to that of primary winding 8. In FIG. 1 it has been assumed that the drive takes place simultaneously so that the voltage present across winding 14 has the shape shown in FIG. 2b. This voltage assumes the value n(V i - V o ) in the period δ T and the value -nVo in the period (1 - δ )T, wherein n is the ratio of the number of turns on windings 14 and 8 and wherein V o is maintained constant at nominal mains voltage V o = δ V inom . However, if as a result of an increase or a decrease of the mains voltage V i increases or decreases proportionally therewith, i.e., V i = V i nom + Δ V, the positive portion of V 14 becomes equal to n(V i nom - V o +Δ V) = n [(1 -δ)V i nom +ΔV] = n(0.5 V inom +ΔV) if δ = 0.5 for V i = V i nom. Relatively, this is a variation which is twice as great. For example, if V i nom = 270 V and V o = 135 V, a variation in the mains voltage of from -15 to +10 percent causes a variation of V i of from -40.5 V to +27 V which ranges from -30 to +20 percent of 135 V which is present across winding 8 during the period δ T. The result is that transistor 16 can always be bottomed over a large range of variation. If the signal of FIG. 2b would be applied through a resistor to the base of transistor 16, the base current thereof would have to undergo the same variation while the transistor would already be saturated in case of too low a voltage. In this case it is assumed that transformer 9 is ideal (without loss) and that coil 21 has a small inductance as is explained in the U.S. patent application Ser. No. 737,009 above mentioned. It is therefore found to be desirable to limit the base current of transistor 16.

stors are simultaneously bottomed, that is during the period δ T. This depends on the winding sense of secondary winding 14 relative to that of primary winding 8. In FIG. 1 it has been assumed that the drive takes place simultaneously so that the voltage present across winding 14 has the shape shown in FIG. 2b. This voltage assumes the value n(V i - V o ) in the period δ T and the value -nVo in the period (1 - δ )T, wherein n is the ratio of the number of turns on windings 14 and 8 and wherein V o is maintained constant at nominal mains voltage V o = δ V inom . However, if as a result of an increase or a decrease of the mains voltage V i increases or decreases proportionally therewith, i.e., V i = V i nom + Δ V, the positive portion of V 14 becomes equal to n(V i nom - V o +Δ V) = n [(1 -δ)V i nom +ΔV] = n(0.5 V inom +ΔV) if δ = 0.5 for V i = V i nom. Relatively, this is a variation which is twice as great. For example, if V i nom = 270 V and V o = 135 V, a variation in the mains voltage of from -15 to +10 percent causes a variation of V i of from -40.5 V to +27 V which ranges from -30 to +20 percent of 135 V which is present across winding 8 during the period δ T. The result is that transistor 16 can always be bottomed over a large range of variation. If the signal of FIG. 2b would be applied through a resistor to the base of transistor 16, the base current thereof would have to undergo the same variation while the transistor would already be saturated in case of too low a voltage. In this case it is assumed that transformer 9 is ideal (without loss) and that coil 21 has a small inductance as is explained in the U.S. patent application Ser. No. 737,009 above mentioned. It is therefore found to be desirable to limit the base current of transistor 16.This may be effected by providing a coil 22 having a large value inductance, approximately 100 μH, between winding 14 and the small coil 21. The variation of said base current i b is shown in FIG. 2c but not to the same scale as the collector current of FIG. 2a. During the conducting interval δ T current i b varies as a linear function of time having a final value of wherein L represents the inductance of coil 22. This not only provides the advantage that this final value is not immediately reached, but it can be shown that variation of this final value as a function of the mains voltage has been reduced, for there applies at nominal mains voltage that: If the mains voltage V i = V i nom +Δ V, then ##SPC1## because V i nom = 2 V o . Thus this variation is equal to that of the mains voltage and is not twice as great.

During switching off, t 2 , of transistor 16 coil 22 must exert no influence and coil 21 must exert influence which is achieved by arranging a diode 23 parallel to coil 22. Furthermore the control circuit of transistor 16 in this example comprises the two diodes 24 and 25 as described in U.S. application Ser. No. 26,497 above referred to, wherein one of these diodes, diode 25 in FIG. 1, must be shunted by a resistor.

During switching off, t 2 , of transistor 16 coil 22 must exert no influence and coil 21 must exert influence which is achieved by arranging a diode 23 parallel to coil 22. Furthermore the control circuit of transistor 16 in this example comprises the two diodes 24 and 25 as described in U.S. application Ser. No. 26,497 above referred to, wherein one of these diodes, diode 25 in FIG. 1, must be shunted by a resistor.The control circuit of transistor 16 may alternatively be formed as is shown in FIG. 4. In fact, it is known that coil 21 may be replaced by the parallel arrangement of a diode 21' and a resistor 21" by which the inverse current can be limited. To separate the path of the inverse current from that of the forward current the parallel arrangement of a the diode 29' and a resistor 29" must then be present. This leads to the circuit arrangement shown in the upper part of FIG. 4. This circuit arrangement may now be simplified if it is noted that diodes 25 and 21' on the one hand and diodes 23 and 29' on the other hand are series-arranged. The result is shown in the lower part of FIG. 4 which, as compared with the circuit arrangement of FIG. 1, employs one coil less and an additional resistor.

F

IG. 3 shows possible modifications of the chopper. FIG. 3a shown in a simplified form the circuit arrangement according to FIG. 1 wherein the pulsatory voltage present across the connections of windings 8 has a peak-to-peak amplitude of V i - V o = 0.5 V i for δ = 0.5, As has been stated, the provision of coil 22 gives a relative variation for the base current of transistor 16 which is equal to that of the mains voltage. In the cases according to FIG. 3b, 3c and 3d the peak-to-peak amplitude of the voltage across winding 8 is equal to V i so that the provision of coil 22 results in a relative variation which is equal to half that of the mains voltage which is still more favorable than in the first case.

Transistors of the npn type are used in FIG. 3. If transistors of the pnp type are used, the relevant efficiency diodes must of course be reversed.

Transistors of the npn type are used in FIG. 3. If transistors of the pnp type are used, the relevant efficiency diodes must of course be reversed.In this connection it is to be noted that it is possible to obtain an output voltage V o with the aid of the modifications according to FIGS. 3b, c and d, which voltage is higher than input voltage V i . These modifications may be used in countries such as, for example, the United of America or France where the nominal mains voltage is 117 or 110 V without having to modify the rest of the circuit arrangement.

The above-mentioned remark regarding the sum of the diode currents only applies, however, for the modifications shown in FIGS. 3a and d.

If line output transistor 16 is not simultaneously driven with switching transistor 2, efficiency diodes 7 conducts simultaneously with transistor 16 i.e., during the period which is denoted by δ T in FIGS. 1 and 2b. During that period the output voltage V o of the chopper is stabilized so that the base current of transistor 16 is stabilized without further difficulty. However, a considerable drawback occurs. In FIG. 1 the reference numeral 26 denotes a safety circuit the purpose of which is to safeguard switching transistor 2 when the current supplied to load 11 and/or line deflection circuit 17 becomes to high, which happens because the chopper stops. After a given period output voltage V o is built up again, but gradually which means that the ratio δ is initially small in the order of 0.1. All this is described in U.S. patent No. 3,629,686. The same phenomenon occurs when the display device is switched on. Since δ = 0.1 corresponds to approximately 6 μs when T = 64 μs, efficiency diode 7 conducts in that case for 64 - 6 = 58 μus so that transistor 16 is already switched on at the end of the scan or at a slightly greater ratio δ during the flyback. This would cause an inadmissibly high dissipation. For this reason the simultaneous drive is therefore to be preferred.

The line deflection circuit itself is also safeguarded: in fact, if something goes wrong in the supply, the driver voltage of the line deflection circuit drops out because the switching voltage across the terminals of primary winding 8 is no longer present so that the deflection stops. This particularly happens when switching transistor 2 starts to constitute a short-circuit between emitter and collector with the result that the supply voltage V o for the line deflection circuit in the case of FIG. 1 becomes higher, namely equal to V i . However, the line output transformer is now cut off and is therefore also safe as well as the picture display tube and other parts of the display device which are fed by terminal 15 or the like. However, this only applies to the circuit arrangement according to FIG. 1 or 3a.

Pulse oscillator 6 applies pulses of line frequency to modulator 5. It may be advantageous to have two line frequency generators as already described, to wit pulse oscillator 6 and line oscillator 6' which is present in the picture display device and which is directly synchronized in known manner by line synchronizing pulses 7'. In fact, in this case line oscillator 6' applies a signal of great amplitude and free from interference to pulse oscillator 6. However, it is alternatively possible to combine pulse oscillator 6 and line oscillator 6' in one single oscillator 6" (see FIG. 1) which results in an economy of components. It will be evident that line oscillator 6' and oscillator 6" may alternatively be synchronized indirectly, for example, by means of a phase discriminator. It is to be noted neither pulse oscillator 6, line oscillator 6' and oscillator 6" nor modulator 5 can be fed by the supply described since output voltage V o is still not present when the mains voltage is switched on. Said circuit arrangements must therefore be fed directly from the input terminals. If as described above these circuit arrangements are to be separated from the mains, a small separation transformer can be used whose primary winding is connected between the mains voltage terminals and whose secondary winding is connected to ground at one end and controls a rectifier at the other end.

Pulse oscillator 6 applies pulses of line frequency to modulator 5. It may be advantageous to have two line frequency generators as already described, to wit pulse oscillator 6 and line oscillator 6' which is present in the picture display device and which is directly synchronized in known manner by line synchronizing pulses 7'. In fact, in this case line oscillator 6' applies a signal of great amplitude and free from interference to pulse oscillator 6. However, it is alternatively possible to combine pulse oscillator 6 and line oscillator 6' in one single oscillator 6" (see FIG. 1) which results in an economy of components. It will be evident that line oscillator 6' and oscillator 6" may alternatively be synchronized indirectly, for example, by means of a phase discriminator. It is to be noted neither pulse oscillator 6, line oscillator 6' and oscillator 6" nor modulator 5 can be fed by the supply described since output voltage V o is still not present when the mains voltage is switched on. Said circuit arrangements must therefore be fed directly from the input terminals. If as described above these circuit arrangements are to be separated from the mains, a small separation transformer can be used whose primary winding is connected between the mains voltage terminals and whose secondary winding is connected to ground at one end and controls a rectifier at the other end.Capacitor 27 is arranged parallel to efficiency diode 7 so as to reduce the dissipation in switching transistor 2. In fact, if transistor 2 is switched off by the pulsatory control voltage, its collector current decreases and its collector-emitter voltage increases simultaneously so that the dissipated power is not negligible before the collector current has becomes zero. If efficiency diode 7 is shunted by capacitor 27 the increase of the collector-emitter voltage is delayed i.e., this voltage does not assume high values until the collector current has already been reduced. It is true that in that case the dissipation in transistor 2 slightly increases when it is switched on by the pulsatory control voltage but on the other hand since the current flowing through diode 7 has decreased due to the presence of the secondar

y windings, its inverse current is also reduced when transistor 2 is switched on and hence its dissipation has become smaller. In addition it is advantageous to delay these switching-on and switching-off periods to a slight extent because the switching pulses then contain fewer Fourier components of high frequency which may cause interferences in the picture display device and which may give rise to visible interferences on the screen of the display tube. These interferences occupy a fixed position on the displayed image because the switching frequency is the line frequency which is less disturbing to the viewer. In a practical circuit wherein the line frequency is 15,625 Hz and wherein switching transistor 2 is an experimental type suitable for a maximum of 350 V collector-emitter voltage or 1 A collector current and wherein efficiency diode 7 is of the Philips type BA 148 the capacitance of capacitor 27 is approximately 680 pF whilst the load is 70 W on the primary and 20 W on the secondary side of transformer 9. The collector dissipation upon switching off is 0.3 W (2.5 times smaller than without capacitor 27) and 0.7 W upon switching on.

As is known the so-called pincushion distortion is produced in the picture display tubes having a substantially flat screen and large deflection angles which are currently used. This distortion is especially a problem in color television wherein a raster correction cannot be brought about by magnetic means. The correction of the so-called East-West pincushion distortion i.e., in the horizontal direction on the screen of the picture display tube can be established in an elegant manner with the aid of the circuit arrangement according to the invention. In fact, if the voltage generated by comparison circuit 12 and being applied to modulator 5 for duration-modulating pulsatory voltage 3 is modulated by a parabola voltage 28 of field frequency, pulsatory voltage 3 is also modulated thereby. If the power consumption of the line deflection circuit forms part of the load on the output voltage of the chopper, the signal applied to the line deflection coils is likewise modulated in the same manner. Conditions therefore are that the parabola voltage 28 of field frequency has a polarity such that the envelope of the sawtooth current of line frequency flowing through the line deflection coils has a maximum in the middle of the scan of the field period and that charge capacitor 10 has not too small an impedance for the field frequency. On the other hand the other supply voltages which are generated by the circuit arrangement according to the invention and which might be hampered by this component of field frequency must be smoothed satisfactorily.

A practical embodiment of the described example with the reference numerals given provides an output for the supply of approximately 85 percent at a total load of 90 W, the internal resistance for direct current loads being 1.5 ohms and for pulsatory currents being approximately 10 ohms. In case of a variation of ± 10 percent of the mains voltage, output voltage V o is stable within 0.4 V. Under the nominal circumstances the collector dissipation of switching transistor 2 is approximately 2.5 W.

Since the internal resistance of the supply is so small, it can be used advantageously, for example, at terminal 15 for supplying a class-B audio amplifier which forms part of the display device. Such an amplifier has the known advantages that its dissipation is directly proportional to the amplitude of the sound to be reproduced and that its output is higher than that of a class-A amplifier. On the other hand a class-A amplifier consumes a substantially constant power so that the internal resistance of the supply voltage source is of little importance. However, if this source is highly resistive, the supply voltage is modulated in the case of a class-B amplifier by the audio information when the sound intensity is great which may detrimentally influence other parts of the display device. This drawback is prevented by means of the supply according to the invention.

The 50 Hz ripple voltage which is superimposed on the rectified input voltage V i is compensated by comparison circuit 12 and modulator 5 since this ripple voltage may be considered to be a variation of input voltage V i . A further compensation is obtained by applying a portion of this ripple voltage with suitable polarity to comparison circuit 12. It is then sufficient to have a lower value for the smoothing capacitor which forms part of rectifier circuit 1 (see FIG. 3). The parabola voltage 28 of field frequency originating from the field time base is applied to the same circuit 12 so as to correct the East-West pincushion distortion.

SABA ULTRACOLOR T56Q75 QUARTZ COMPUTER CHASSIS Q110 Regulated deflection circuit:

A

deflection generator of a television receiver is coupled to a deflection winding for generating scanning current during a deflection cycle. The generator includes a retrace capacitor coupled to the deflection winding for forming a retrace resonant circuit therewith to produce a retrace pulse voltage during a retrace interval of the deflection cycle. An inductor and another capacitor form a second resonant circuit that is coupled to the retrace resonant circuit. A switching arrangement is coupled to a source of energy and the second resonant circuit in a push-pull configuration. The switching arrangement is responsive to a deflection rate switching signal to store during trace a controllable amount of energy from the source in the second resonant circuit. This stored energy is then transferred to the retrace resonant circuit during the retrace interval to replenish losses sustained during the deflection cycle.

1. A deflection circuit comprising:

a deflection winding;

a deflection generator coupled to said deflection winding for generating scanning current in said deflection winding during a deflection cycle, said deflection generator including a retrace capacitance coupled to said deflection winding for forming a retrace resonant circuit therewith to produce a retrace pulse voltage during a retrace interval of said deflection cycle;

an inductance;

a second capacitance coupled to said inductance for forming a second resonant circuit therewith, said second resonant circuit being coupled to said deflection generator;

a source of energy; and

switching means coupled to said source and to said second resonant circuit in a self-oscillating configuration, said switching means being responsive to a deflection rate switching signal for storing a controllable amount of energy from said source in said second resonant circuit, said retrace pulse voltage being applied to said second resonant circuit to provide for the transfer of energy between said second and retrace resonant circuits,

said switching means in the absence of said deflection rate switching signal undergoing free-running oscillation.

2. A deflection circuit according to claim 1 wherein said switching means is coupled to said source and to said second resonant circuit in a blocking oscillator configuration. 3. A deflection circuit according to claim 2 wherein the frequency of said free-running oscillation is lower than the frequency of said deflection cycle. 4. A deflection circuit according to claims 1 or 2 wherein said switching means includes first and second switching devices coupled to said inductance in a push-pull relationship. 5. A deflection circuit according to claim 4 wherein the frequency of free-running oscillation is such that during said free-running oscillation, each of said first and second switching devices conducts for a duration that is longer than the duration of said trace interval. 6. A deflection circuit according to claim 5 wherein the amount of energy stored in said second resonant circuit at the end of said trace interval remains substantially unchanged as said controllable instant varies. 7. A deflection circuit according to claim 1 wherein said switching arrangement includes a first controllable switching device coupled to said source and to said second resonant circuit, a second controllable switching device coupled to said second resonant circuit, and a control circuit responsive to said deflection rate signal for changing the conductive state of said first switching device at a controllable instant within the trace interval of said deflection cycle and of said second switching device within said retrace interval. 8. A deflection circuit according to claim 7 wherein said control circuit is responsive to a deflection circuit energy level to vary said controllable instant as said energy level varies. 9. A deflection circuit according to claim 8 wherein the amount of energy stored in said second resonant circuit at the end of said trace interval remains substantially unchanged as said controllable instant varies. 10. A deflection circuit according to claims 1, 7 or 9 wherein said second resonant circuit is coupled to said deflection generator by way of a transformer, a first winding thereof being coupled to said second resonant circuit, a second winding thereof being coupled to said retrace resonant circuit. 11. A deflection circuit according to claim 7 wherein said first and second controllable switching devices include first and second bidirectionally conductive main current paths, respectively, the two main current paths being coupled in series across said source of energy, said inductance and said second capacitance being coupled in series across one of said two main current paths. 12. A deflection circuit according to claim 11 wherein said second resonant circuit is coupled to said deflection generator by way of a flyback transformer, a first winding thereof being coupled in series with said inductance and second capacitance across said one main current path, a second winding thereof being coupled to said retrace resonant circuit. 13. A deflection circuit according

to claims 7 or 9 wherein said inductance includes a main winding coupled to a main current path of each of said two controllable switches and two control windings, each coupled respectively to a control terminal of a respective switch. 14. A deflection circuit according to claim 9 wherein said control circuit includes means for detecting an overload condition and means for establishing said controllable instant at a point within the deflection cycle where the amount of energy transferred by said second resonant circuit is substantially reduced. 15. A deflection circuit according to claim 1 wherein said switching arrangement includes first and second controllable switches having their main current paths coupled to said inductance and control means for alternately turning off said two switches, said control means including means for maintaining the main current path of a given switch nonconductive until after conduction is substantially cut off in the main current path of the other switch. 16. A deflection circuit according to claim 15 wherein said control means includes a capacitance coupled to said inductance for providing a path for current to flow from said inductance, other than through a main path of eit

her of the two controllable switches, during the time that the conduction in the main current path of either of the two switches is being cut off. 17. A deflection circuit according to claim 1 wherein said deflection generator includes a controllable output device coupled to said deflection winding, a deflection oscillator coupled to a control terminal of said output device for switching said output device on within the trace interval of said deflection cycle and for switching said output device off to initiate said retrace interval, means for detecting oscillation of said retrace resonant circuit, and means coupled to said deflection oscillator and to said detecting means for maintaining said output device off when oscillation of said retrace resonant circuit is detected. 18. A deflection circuit according to claim 17 wherein said second resonant circuit is coupled to said deflection generator by way of a transformer, a first winding thereof being coupled to said second resonant circuit, a second winding thereof being coupled to said retrace resonant circuit, a third winding thereof comprising said detecting means. 19. A deflection circuit, comprising:

her of the two controllable switches, during the time that the conduction in the main current path of either of the two switches is being cut off. 17. A deflection circuit according to claim 1 wherein said deflection generator includes a controllable output device coupled to said deflection winding, a deflection oscillator coupled to a control terminal of said output device for switching said output device on within the trace interval of said deflection cycle and for switching said output device off to initiate said retrace interval, means for detecting oscillation of said retrace resonant circuit, and means coupled to said deflection oscillator and to said detecting means for maintaining said output device off when oscillation of said retrace resonant circuit is detected. 18. A deflection circuit according to claim 17 wherein said second resonant circuit is coupled to said deflection generator by way of a transformer, a first winding thereof being coupled to said second resonant circuit, a second winding thereof being coupled to said retrace resonant circuit, a third winding thereof comprising said detecting means. 19. A deflection circuit, comprising: a deflection winding;

a deflection generator coupled to said deflection winding for generating scanning current in said deflection winding during a deflection cycle, said deflection generator including a retrace capacitance coupled to said deflection winding for forming a retrace resonant circuit therewith to develop a retrace pulse voltage during a retrace interval of said deflection cycle;

a second resonant circuit including an inductance, said retrace pulse applied voltage being applied thereto;

a source of input voltage;

first and scond controllable switches coupled to said second resonant circuit, each switch becoming conductive after the other switch becomes substantially nonconductive, said first switch when conductive coupling said source of input voltage to said second resonant circuit to enable the transfer of energy between said source and said second resonant circuit and when nonconductive decoupling said source from said second resonant circuit, said second switch when conductive enabling the transfer of energy between said second resonant circuit and said retrace resonant circuit.

20. A deflection circuit according to claim 19 wherein said first and second switches are coupled to said inductance in a push-pull relationship. 21. A deflection circuit according to claims 19 or 20 including control means coupled to control terminals of said first and second switches and responsive to a deflection circuit energy level and a deflection rate control signal for turning off said second switch at an instant within the trace interval of said deflection cycle that varies as said energy level varies to provide regulation thereof and for turning off said first switch near the beginning of the retrace interval. 22. A deflection circuit according to claim 21 wherein said two switches are bidirectionally conductive. 23. A deflection circuit according to claim 21 wherein said inductance includes a main winding coupled to output terminals of said first and second switches and first and second control windings coupled to the respective control terminals of said first and second switches to provide regenerative feedback of the voltages at said output terminals. 24. A deflection circuit according to claim 23 wherein, in the absence of said deflection rate control signal, said regenerative feedback produces oscillation of the voltages at said output terminals at a frequency lower than the frequency of said deflection cycle. 25. A deflection circuit according to claim 24 wherein said deflection generator includes a controllable output device coupled to said deflection winding, a deflection oscillator coupled to a control terminal of said output device for switching said output device on within the trace interval of said deflection cycle and for switching said output device off to initiate said retrace interval, means for detecting oscillation of said retrace resonant circuit, and means coupled to said deflection oscillator and to said detecting means for maintaining said output device off when oscillation of said retrace resonant circuit is detected. 26. A deflection circuit according to claim 21 wherein said control means includes means for detecting an overload condition within

said deflection circuit, means responsive to the detected overload condition for establishing the instant within the trace interval that said second switch is turned off at an instant that provides substantially reduced energy transfer to said retrace resonant circuit. 27. A deflection circuit according to claims 19 or 20 wherein said second resonant circuit includes a capacitance, said first switch when conductive applying said input voltage across the series arrangement of said second resonant circuit capacitance and said inductance. 28. A deflection circuit according to claim 27 including a flyback transformer having a first winding coupled to said second switch and a second winding coupled to said retrace resonant circuit for developing a retrace pulse voltage across said flyback tranformer first winding, said second switch when conductive applying said retrace pulse voltage across said series arrangement. 29. A deflection circuit, comprising:

said deflection circuit, means responsive to the detected overload condition for establishing the instant within the trace interval that said second switch is turned off at an instant that provides substantially reduced energy transfer to said retrace resonant circuit. 27. A deflection circuit according to claims 19 or 20 wherein said second resonant circuit includes a capacitance, said first switch when conductive applying said input voltage across the series arrangement of said second resonant circuit capacitance and said inductance. 28. A deflection circuit according to claim 27 including a flyback transformer having a first winding coupled to said second switch and a second winding coupled to said retrace resonant circuit for developing a retrace pulse voltage across said flyback tranformer first winding, said second switch when conductive applying said retrace pulse voltage across said series arrangement. 29. A deflection circuit, comprising: means for developing an input voltage between first and second input terminals;

first and second controllable switches, each having a main current path and a control terminal for controlling conduction therein, the two main current paths being coupled together at an output terminal and further being coupled in a series arrangement between said first and second input terminals;

a first resonant circuit including an inductance coupled between said output terminal and one of said first and second input terminals;

a deflection winding;

a deflection generator coupled to said deflection winding for generating scanning current in said deflection winding during a deflection cycle and further including a retrace resonant circuit that directly applies a retrace pulse voltage to said first resonant circuit;

a control circuit coupled to the control terminals of both switches for alternately turning off conduction in the main paths of said two switches during a deflection cycle to store energy in said inductance that is transferred to said retrace resonant circuit during application of said retrace pulse voltage to said first resonant circuit; and

a capacitance coupled between said output terminal and one of said first and second input terminals to accept the flow of current from said inductance when conduction in the main path of one switch is being turned off and prior to the commencement of conduction in the the main path of the other switch to avoid any significant simultaneous conduction in the main paths of both switches.

30. A deflection circuit according to claim 29 including a voltage divider having first and second end terminals coupled respectively to said first and second input terminals, having a third terminal intermediate the two voltage divider end terminals coupled to said output terminal, having a fourth terminal intermediate one of said voltage divider end terminals and said voltage divider third terminal coupled to the control terminal of one of said switches, and having a fifth terminal intermediate the other one of said voltage divider end terminals and said voltage divider third terminal coupled to the control terminal of the other one of said switches. 31. A deflection circuit according to claim 29 wherein said deflection generator includes a retrace capacitance coupled to said deflection winding for forming a retrace resonant circuit therwith to generate a retrace pulse voltage during a retrace interval of said deflection cycle, said retrace resonant circuit being coupled to said first resonant circuit during the retrace interval to transfer energy therebetween. 32. A deflection circuit according to claim 31 wherein the first resonant circuit is coupled to said deflection generator by way of a flyback transformer, a first winding thereof being coupled to said first resonant circuit, a second winding thereof being coupled to said retrace resonant circuit. 33. A deflection circuit according to claim 31 wherein said control circuit includes means for regneratively feeding back the voltage at said output terminal to produce free-running oscillation of said switching means in the absence of retrace pulse generation. 34. A deflection circuit according to claim 33 wherein said first resonant circuit includes a capacitance coupled in series with said inductance between said output terminal and said one input terminal. 35. A deflection circuit, comprising:

a deflection winding;

a deflec

tion generator coupled to said deflection winding for generating scanning current in said deflection winding during a deflection cycle, said deflection generator including a retrace capacitance coupled to said deflection winding for forming a retrace resonant circuit therewith to produce a retrace pulse voltge during a retrace interval of said deflection cycle;

an inductance coupled to said deflection generator;

a source of energy;

switching means coupled to said source and to said inductance and responsive to a deflection rate switching signal for storing a controllable amount of energy from said source in said inductance, said retrace pulse voltage being applied to said inductance to provide for the transfer of energy between said inductance and said retrace resonant circuit; and

means for regeneratively feeding back the output of said switching means to produce free-running oscillation thereof in the absence of said deflection rate switching signal.

Known AC power line or mains isolated television receivers show a variety of design approaches for the power supply circuitry. In one design, a 50 or 60 cycle mains transformer may be used to provide electrical isolation. The mains transformer, however, is relatively heavy and bulky. The magnetic stray field produced by the transformer may introduce purity registration errors in a color television receiver. Furthermore, since the mains transformer provides only electrical isolation, additional voltage regulation circuitry may be needed.

A switched mode power supply may be used in large screen television receivers. Such a power supply is relatively costly and requires special components such as the switched mode transformer, switching transistor and rectifier diodes. The control circuit may include overload and short circuit protection and therefore be complicated and difficult to service and prone to increased failure rates. Where the high voltage or flyback transformer is used for mains isolation in a synchronously switched type power supply, a complicated control circuit may be required as well as a separate power supply for television receiver start-up.

A feature of the invention is a switching power supply requiring no specialized components and using simplified control circuitry. The power supply provides intrinsic protection against overloads and short circuits and does not require a separate start-up transformer.

A deflection generator is coupled to a deflection winding for generating scanning current during a deflection cycle. The deflection generator includes a retrace capacitance coupled to the deflection winding for forming a retrace resonant circuit therewith to produce a retrace pulse voltage during a retrace interval of the deflection cycle. A second resonant circuit including an inductance is coupled to the retrace resonant circuit to enable energy to be transferred therebetween. A switching arrangement is coupled to a source of energy and to the second resonant circuit and is responsive to a deflection rate switching signal for storing a controllable amount of energy from the source in the second resonant circuit.

In one inventive aspect, the switching arrangement forms a self-oscillating arrangement with the second resonant circuit to produce free-running oscillation, in the absence of the deflection rate switching signal. Such an arrangement provides for soft-start operation and limited energy transfer during short-circuit conditions.

In another inventive aspect, the switching arrangement comprises first and second controllable switches coupled to the second resonant circuit. Each switch becomes conductive after the other switch has become nonconductive. The first switch when conductive couples the source of energy to the second resonant circuit to enable the transfer of energy therebetween. The first switch when nonconductive decouples the source from the second resonant circuit. The second switch when conductive enables the transfer of energy between the second resonant circuit and the retrace resonant circuit.

FIGS. 1a and 1b illustrate in simplified schematic form two embodiments of a regulated deflection circuit embodying the invention;

FIGS. 2a and 2b illustrate a detailed embodiment of a regulated deflection circuit embodying the invention;

FIG. 3 illustrates an embodiment of a regulator control circuit for the circuit of FIGS. 2a and 2b;

FIG. 4 illustrates waveforms associated with the operation of the regulator control circuit of FIG. 3;

FIGS. 5-12 illustrate waveforms associated with the operation of the circuits of FIGS. 1a, 1b, 2a and 2b;

FIG. 13 illustrates another embodiment of a regulator control circuit for the circuit of FIGS. 2a and 2b; and

FIGS. 14 and 15 illustrate waveforms associated with the operation of the circuit of FIG. 13.

In the Drawing figures, the convention chosen for the direction of the voltage arrow between two terminals is such that the negative terminal is considered the reference terminal nearest which the tail of the arrow is located.

FIGS. 1

a and 1b illustrate in simplified schematic form a regulated television receiver deflection circuit and power supply embodying the invention. FIG. 1a illustrates a version not conductively isolated from the AC power mains source and FIG. 1b illustrates an isolated version. Switching devices S1 and S2 form a blocking oscillator arrangement 30 with an inductor L1 and a capacitor C5. The conduction of both switches is controlled by a positive feedback signal, not illustrated in FIGS. 1a and 1b, derived from the voltage developed across inductor L1 and provided to a regulator control circuit 26. Included in FIGS. 1a and 1b are the mains supply rectifier 24 with its filter capacitor C1, the horizontal deflection circuit 60, and the flyback transformer T1. Not illustrated in FIGS. 1a and 1b are the various load circuits of the television receiver that are coupled to windings of the flyback transformer.

a and 1b illustrate in simplified schematic form a regulated television receiver deflection circuit and power supply embodying the invention. FIG. 1a illustrates a version not conductively isolated from the AC power mains source and FIG. 1b illustrates an isolated version. Switching devices S1 and S2 form a blocking oscillator arrangement 30 with an inductor L1 and a capacitor C5. The conduction of both switches is controlled by a positive feedback signal, not illustrated in FIGS. 1a and 1b, derived from the voltage developed across inductor L1 and provided to a regulator control circuit 26. Included in FIGS. 1a and 1b are the mains supply rectifier 24 with its filter capacitor C1, the horizontal deflection circuit 60, and the flyback transformer T1. Not illustrated in FIGS. 1a and 1b are the various load circuits of the television receiver that are coupled to windings of the flyback transformer. To describe the free-running operation of blocking oscillator 30 of FIG. 1a, for example, assume horizontal trace switch 35 of horizontal deflection circuit 60 is shortcircuited to ground. Blocking oscillator 30 will free-run at a frequency determined by the values of L1 and C5. This frequency may be chosen about 2 or more times lower than the horizontal deflection frequency, f H . The free-running frequency is selected lower than the horizontal deflection frequency in order to permit proper synchronization of blocking oscillator operation with horizontal scanning current generation when the blocking oscillator operates in the deflection synchronized mode. However, if the free-running frequency is selected too low, unnecessarily high peak currents in inductor L1 are developed during free-running operation.

The choice of the L to C ratio of inductor L1 and capacitor C5 determines the peak input current or inductor current i L that will flow during free-running operation and therefore determines the maximum available power that can be consumed. Free-running operation also occurs in case of a short-circuited load being produced across any of the windings of flyback transformer T1.

The switching voltage V S2 across switch S2 and the inductor current i L flowing during free-running operation

is illustrated in FIGS. 5a and 5b. The voltage switching waveform across switch S1, not illustrated, is 180° out of phase with the waveform of FIG. 5a. Most of the power flowing through the two switches is reactive in nature and, thus, the actual power consumption is very low. The power consumption equals the losses in switches S1 and S2 and in the resistive components of inductor L1 and capacitor C5.

is illustrated in FIGS. 5a and 5b. The voltage switching waveform across switch S1, not illustrated, is 180° out of phase with the waveform of FIG. 5a. Most of the power flowing through the two switches is reactive in nature and, thus, the actual power consumption is very low. The power consumption equals the losses in switches S1 and S2 and in the resistive components of inductor L1 and capacitor C5. To describe synchronized oscillator operation, assume that horizontal output transistor Q10 of FIG. 1a is being switched at a horizontal rate to generate scanning current in horizontal deflection winding L H and that a retrace pulse voltage V r , illustrated in FIG. 6a, is being generated at the collector electrode of output transistor Q10. From time t 2 within the horizontal trace interval of FIGS. 6a-6c to the later time t 0 , the beginning of the next horizontal retrace interval, switch S2 is open and switch S1 is closed. The inductor current i L flows through switch S1, inductor L1, capacitor C5 and trace switch 35 to ground. At time t 0 , the energy, I p1 2 L/2, is stored in inductor L1 where L is the inductance of inductor L1 and I p1 is the peak current flowing in inductor L1 at time t 0 .

At time t 0 of FIGS. 6a-6c, horizontal output transistor Q10 opens. The developed retrace pulse voltage V r is applied to regulator control circuit 26 along a signal line s to synchronize the opening of switch S1 and closing of switch S2 with the beginning of horizontal retrace. With switch S2 closed between times t 0 -t 2 , the current path for the inductor current i L is now connected to the retrace resonant circuit 50, comprising retrace capacitor C R , S-shaping capacitor C S and horizontal deflection winding L H . As a result, the energy stored in inductor L1 at time t 0 transfers rapidly into the retrace resonant circuit 50, as illustrated by the rapidly decreasing current i L after time t 0 in FIG. 6c. The current i L decreases rapidly, and when it reaches zero, all the energy stored in inductor L1 has been transferred. Subsequent to the zero-crossover instant of the inductor current i L during retrace, a small portion of the transferred energy returns to inductor L1 as indicated by the negative current i L prior to time t 1 . At time t 1 , the end of the horizontal retrace interval, damper diode D d and the base-collector junction of output transistor Q10 become forward biased, again effectively coupling capacitor C5 to ground. The energy transferred during each horizontal deflection cycle is substantially the difference between the energies stored in inductor L1 at times t 0 and t 1 .

Between times t 1 and t 2 , the current i L circulates through switch S2, inductor L1, capacitor C5 and the now closed trace switch 35. During this interval, energy stored in capacitor C5 discharges back into inductor L1. At time t 2 , regulator control circuit 26 opens switch S2 and closes switch S1. The stored energy in inductor L1 now transfers back into the main filter capacitor C1 until the zero-crossover instant t 3 of the inductor current i L . From time t 3 until the beginning of the next retrace interval, energy is again stored in indcutor L1 for subsequent transferral to retrace resonant circuit 50 and to the load circuits coupled to the various windings of flyback transformer T1.

T

he righthand side waveforms of FIGS. 6a-6c illustrate deflection synchronized operation of blocking oscillator 30 at a lower loading level by the load circuits coupled to the various windings of flyback transformer T1 when compared to the loading level illustrative of the lefthand side waveforms. The regulation action is to maintain the peak amplitude of retrace pulse V r constant. At the lower loading level, in contrast to the previously described situation, more energy has returned to inductor L1 at the end of the horizontal retrace interval, at time t 1 ', and more energy is to be returned to the mains filter capacitor C1 from time t 2 ' as a result of the lower consumption by the television receiver load circuits.

It should be noted that the energies stored in inductor L1 at time t 0 of the lefthand side waveforms of FIGS. 6a-6c and at time t 0 ' of the righthand side waveforms are substantially equal, independent of the degree of loading. The peak stored energy depends only upon the rectified mains voltage amplitude. The maximum power than can be transferred by blocking oscillator 30 is therefore limited. At maximum loading or during short-circuit load operation, the average voltage across capacitor C5 is approximately half the magnitude of the input voltage Vin. With decreasing load, the average voltage across capacitor C5 increases.

The operation of the circuit of FIG. 1b is similar to that of the operation of the circuit of FIG. 1a because electrically they are substantially equivalent, due to the tight coupling between windings W1 and W2 of transformer T1 in FIG. 1b. A winding W6 of flyback transformer T1 develops the retrace pulse voltage that is applied to regulator control circuit 26 along signal line s.

FIGS. 2a and 2b illustrate a detailed embodiment of a regulated television receiver deflection circuit embodying the i

nvention. A 220 VAC, 50 Hz, power line or mains supply voltage is applied across terminals 21 and 22, full-wave rectified by rectifier 24, and filtered by a capacitor C1, to develop an unregulated direct input voltage Vin, of illustratively 290 volts, at a terminal 28. A television receiver on/off switch 23 is coupled between terminal 21 and an input terminal of bridge rectifier 24. The current return terminal of the bridge rectifier is coupled to an earth ground 25, not conductively isolated from the mains supply terminals 21 and 22. A current limiting resistor R1 is connected between the output terminal of bridge rectifier 24 and input terminal 28.

nvention. A 220 VAC, 50 Hz, power line or mains supply voltage is applied across terminals 21 and 22, full-wave rectified by rectifier 24, and filtered by a capacitor C1, to develop an unregulated direct input voltage Vin, of illustratively 290 volts, at a terminal 28. A television receiver on/off switch 23 is coupled between terminal 21 and an input terminal of bridge rectifier 24. The current return terminal of the bridge rectifier is coupled to an earth ground 25, not conductively isolated from the mains supply terminals 21 and 22. A current limiting resistor R1 is connected between the output terminal of bridge rectifier 24 and input terminal 28. Unregulated input voltage Vin is applied to a blocking oscillator-regulator 30 that comprises the switching

arrangement of controllable switches S1 and S2 coupled to a resonant circuit 40 in a push-pull relationship. Resonant circuit 40 is formed by the main winding WA of an inductor L1 and a capacitor C5. Switch S1 comprises a transistor Q1 and a damper diode D1 coupled between the collector and emitter electrodes of the transistor. Switch S2 comprises a transistor Q2 and a damper diode D2 coupled between the collector and emitter electrodes of transistor Q2. The main current paths of switches S1 and S2 are therefore bidirectionally conductive and coupled in series across the source of input voltage between terminals 28 and 25. The main current paths of switches S1 and S2 are also coupled to resonant circuit 40 at a common output junction terminal 31 of the switches S1 and S2 and the main winding WA of inductor L1.