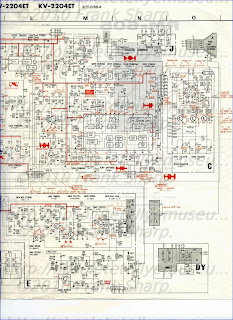

The CHASSIS SCC-216B-A is developed in a multi board fashion.

- Right side EHT + Line deflection + E/W Correction

- Bottom Right Deflection board and FRAME deflection and synchronization

- Bottom center power supply unit

- Left Upside chroma + luma + sound + IF stages.

UPC1365C

Chroma Processor Circuit - PAL Chrominance & Luminance ProcessorSONY KV-2204ET CHASSIS SCC-216B-A CONVERGENCE DEFLECTION SYSTEM FOR A SONY COLOR PICTURE TUBE

In a color picture tube in which a plurality of be

ams are made to intersect each other at a location between the beam generating sources and the color screen and are focused on the latter by a main focusing lens positioned to dispose its optical center substantially at the location where the beams intersect so that beams emerge from such lens along divergent paths, first and second spaced plates are disposed at opposite sides of each of the divergent paths to electrostatically deflect the respective beam and cause convergence of all of the beams at a common area on the screen when the first and second plates are at different potentials, a high voltage is generated from a horizontal deflecting pulse provided for causing the beams to scan the screen and such high voltage is applied to an anode electrode of the tube and also to each first plate, and a static convergence deflecting voltage is obtained by dividing the aforementioned high voltage and is applied as the potential difference between the first and second plates by which the respective beam is to be deflected. Further, a dynamic convergence deflecting voltage, comprising both parabolic and sawtooth voltages is generated in response to the horizontal deflecting pulse and is superimposed on the static convergence deflecting voltage with provision being made for separately adjusting both deflecting voltages.

ams are made to intersect each other at a location between the beam generating sources and the color screen and are focused on the latter by a main focusing lens positioned to dispose its optical center substantially at the location where the beams intersect so that beams emerge from such lens along divergent paths, first and second spaced plates are disposed at opposite sides of each of the divergent paths to electrostatically deflect the respective beam and cause convergence of all of the beams at a common area on the screen when the first and second plates are at different potentials, a high voltage is generated from a horizontal deflecting pulse provided for causing the beams to scan the screen and such high voltage is applied to an anode electrode of the tube and also to each first plate, and a static convergence deflecting voltage is obtained by dividing the aforementioned high voltage and is applied as the potential difference between the first and second plates by which the respective beam is to be deflected. Further, a dynamic convergence deflecting voltage, comprising both parabolic and sawtooth voltages is generated in response to the horizontal deflecting pulse and is superimposed on the static convergence deflecting voltage with provision being made for separately adjusting both deflecting voltages. 1. In a single-gun, plural-beam cathode-ray tube which includes a beam-receiving screen, beam-generating means for directing a plurality of electron beams toward said screen, and lens means for focusing said electron beams on said screen and having an optical center through which said beams are all passed with at least two of said beams emerging from said lens means along paths which are divergent to the optical axis of the latter; electron beam convergence-deflecting means to deflect said beams emerging along said divergent paths for convergence of said beams at a common area of said screen, said convergence-deflecting means comprising first and second spaced plates disposed at opposite sides of each of said divergent paths for electrostatically deflecting the respective beam when at different electrical potentials, high voltage-generating means receiving a horizontal deflecting pulse and operative to generate a high voltage therefrom, means to apply said high voltage as an anode voltage in said tube and also to said first plate associated with each divergent path, voltage-dividing means dividing said high voltage to produce a static convergence deflecting voltage, and means to apply said static convergence voltage between said first plate and said second plate associated with each divergent path and thereby establish the potential difference therebetween for deflecting the respective beam.

2. A single-gun, plural-beam cathode-ray tube according to claim 1, in which said voltage-dividing means includes first and second series connected resistors having said high voltage applied thereacross so that said static convergence-deflecting voltage appears across one of said resistors.

3. A single-gun, plural-beam cathode-ray tube according to claim 2, in which one of said resistors is variable to permit adjustment of said static convergence-deflecting voltage obtained by dividing said high voltage.

4. A single-gun, plural-beam cathode-ray ray tube according to claim 2, in which capacitors are respectively connected in parallel with said first and second resistors for stabilizing the voltages appearing thereacross.

5. A single-gun, plural-beam cathode-ray tube according to claim 2, in which there are provided means to generate a dynamic convergence-deflecting voltage, and means to superimpose said dynamic convergence voltage on said static convergence voltage.

6. A single-gun, plural-beam cathode-ray tube according to claim 5, in which said means to superimpose the dynamic convergence voltage on the static convergence voltage is an isolating transformer connected to said means to generate the dynamic convergence-deflecting voltage and to said voltage-dividing means.

7. A single-gun, plural-beam cathode-ray tube according to claim 6, in which said isolating transformer has a primary winding connected with said means to generate the dynamic convergence-deflecting voltage and a secondary winding connected in series between said first and second resistors of said voltage dividing means.

8. A single-gun, plural-beam cathode-ray tube according to claim 6, in which said isolating transformer has a primary winding connected with said means to generate the dynamic convergence-deflecting voltage and a secondary winding connected at one end to a connecting point between said first and second resistors of said voltage-dividing means and at the other end to said second plate associated with each of said divergent paths.

9. A single-gun, plural-beam cathode-ray tube according to claim 5, in which the tube has a horizontal deflection coil to cause the beams to horizontally scan the screen when a horizontal deflecting current of sawtooth configuration flows through said coil, and in which said means to generate a dynamic convergence-deflecting voltage includes means to derive from said horizontal deflecting current flowing through said coil a voltage of parabolic waveform, means operating in synchronism with said horizontal deflecting current to produce a voltage of sawtooth waveform and means to combine the voltages of parabolic and sawtooth waveform for constituting said dynamic convergence deflecting voltage.

10. A single-gun, plural-beam cathode-ray tube according to claim 9, in which means are provided to separately adjust the magnitude of said voltage of parabolic waveform and the magnitude and wave shape of said voltage of sawtooth waveform.

11. A single-gun, plural-beam cathode-ray tube according to claim 9, in which a capacitor is connected in series with said horizontal deflection coil to produce a voltage of parabolic waveform across said capacitor, capacitive means divides said voltage across said capacitor to provide said voltage of parabolic waveform to be combined with said voltage of sawtooth waveform, and variable inductor means is connected between said capacitance means and said means to superimpose the dynamic convergence voltage on the static convergence voltage to adjust the magnitude of said voltage of parabolic waveform thus combined.

12. A single-gun, plural-beam cathode-ray tube according to claim 11, in which said means to produce the voltage of sawtooth waveform includes a flyback transformer driven in synchronism with said horizontal deflection current and having a secondary winding, a potentiometer having a resistance and a slider movable therealong, and an inductor connected in series with said potentiometer resistance across said secondary winding to produce a voltage of sawtooth configuration across said resistance, with said voltage of sawtooth waveform to be combined with said voltage of parabolic waveform appearing at said slider of the potentiometer.

13. A single-gun, plural-beam cathode-ray tube according to claim 12, in which said means to superimpose said dynamic and static convergence

voltages includes an isolating transformer having a primary winding connected to said slider of the potentiometer and to said variable inductor means.

voltages includes an isolating transformer having a primary winding connected to said slider of the potentiometer and to said variable inductor means. 14. Horizontal dynamic convergence voltage-generating means for a cathode-ray tube having a horizontal deflection coil to effect horizontal beam scanning in response to the passage therethrough of a horizontal deflecting current of sawtooth configuration, comprising means operating in synchronism with said horizontal deflecting current to produce a voltage of sawtooth waveform, a capacitor connected in series with said horizontal deflection coil to produce a first voltage of parabolic waveform across said capacitor, capacitive means dividing said first voltage across said capacitor to provide a second voltage of parabolic waveform, means to combine said second voltage of parabolic waveform with said voltage of sawtooth waveform, and variable inductor means connected between said capacitance means and said means to combine said second voltage of parabolic waveform with said voltage of sawtooth waveform to adjust the magnitude of said second voltage of parabolic waveform thus combined.

15. Horizontal dynamic convergence voltage-generating means according to claim 14, in which said means to produce the voltage of sawtooth waveform includes a flyback transformer driven in synchronism with said horizontal deflection current and having a secondary winding, a potentiometer having a resistance and a slider movable therealong, and an inductor connected in series with said potentiometer resistance across said secondary winding to produce a voltage of sawtooth configuration across said resistance, with said voltage of sawtooth waveform to be combined with said voltage of parabolic waveform appearing at said slider of the potentiometer.

16. Horizontal dynamic convergence voltage-generating means according to claim 15, in combination with means to produce a static convergence-deflecting voltage, and means to superimpose said dynamic convergence-deflecting voltage on said static convergence-deflecting voltage including isolating transformer means having a primary winding connected, at its ends, to said variable inductor means and to said slider, respectively.

In single-gun, plural-beam color picture tubes of the described type, for example, as specifically disclosed in the U.S. Pat. No. 3,448,316, issued June 3, 1969 and having a common assignee herewith, three electron beams are emitted or originated by a beam generating or cathode assembly so that one central beam coincides with the optical axis of the electron focusing lens and the two other beams are converged to cross the central beam substantially at the optical center of the lens and thus emerge from the latter along paths that are divergent from the optical axis. Arranged along opposite sides of each of such divergent paths are first and second convergence-deflecting plates at different electrical potentials to deflect the respective beam for causing all beams to converge at a point on the aperture grill or other beam selecting means associated with the color screen, and from which the beams again diverge to impinge on respective phosphor stripes or dots of the screen. After passing between the convergence-deflecting plates, the beams are acted upon by the magnetic fields resulting from the application of horizontal and vertical sweep signals to the corresponding coils of a deflection yoke, whereby the beams are made to scan the screen in the desired raster. It will be apparent that the accurate convergence of the beams at the aperture grill or other beam-selecting means of the tube is dependent upon the convergence-deflecting voltages applied between the plates.

Accordingly, it is an object of this invention to provide a color picture tube of the described type with an improved circuit arrangement by which the convergence-deflecting voltages are generated.

Another object is to provide a circuit arrangement, as above, which produces a static convergence voltage from a high voltage applied to the tube anode, and wherein variations in the anode voltage are accurately reflected in corresponding charges in the static convergence voltage so as to maintain the proper convergence of the beams.

Another object is to provide a circuit arrangement, as above, which produces a horizontal dynamic convergence voltage superimposed on the static convergence voltage while isolating the source of such dynamic convergence voltage from the static convergence voltage.

Still another object is to provide a circuit arrangement, as above, and in which the static and dynamic convergence voltages can be individually controlled without danger from high voltages.

A further object is to provide a circuit arrangement, as above, with improved means for producing the dynamic convergence voltage.

In accordance with an aspect of this invention, the high voltage applied to an anode electrode of the color picture tube and to one of the convergence deflecting plates associated with each divergent path is generated from a horizontal deflecting pulse provided for causing horizontal scanning of the beams, and the static convergence-deflecting voltage applied between the convergence-deflecting plates associated with each divergent path is obtained by dividing the mentioned high voltage.

Further, in accordance with the invention, the dynamic convergence-deflecting voltage which is superimposed on the static convergence-deflecting voltage is generated in response to the horizontal deflecting pulse.

The above, and other objects, features and advantages of the invention, will be apparent in the following detailed description of illustrative embodiments thereof which is to be read in connection with the accompanying drawings, wherein:

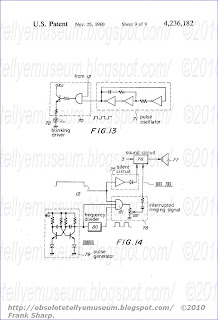

FIG. 1 is a schematic sectional view in a horizontal plane passing through the axis of a single-gun, plural-beam color picture tube and which is shown provided with a convergence deflection system according to one embodiment of this invention;

FIGS. 2A-2E are graphic representations of the wave forms of the static and dynamic convergence deflection voltages produced according to this invention; and

FIG. 3 is a diagrammatic view showing a modification of the convergence deflection system of FIG. 1.

Referring now to the drawings in detail, and initially to FIG. 1 thereof, it will be seen that a single-gun, plural-beam color picture tube of the type to which this invention is applied may comprise a glass envelope (not shown) having a neck and a cone extending from the neck to a color

Screen S provided with the usual arrays of color phosphors S R , S G and S B and with an aperture grill G P or beam-selecting means, such as a so-called shadow mask. Disposed within the neck is a single electron gun A having cathodes K R , K G and K B , each of which is constituted by a beam-generating source with the respective beam-generating surfaces thereof disposed as shown in a plane which is substantially perpendicular to the axis of the electron gun. In the embodiment shown, the beam-generating surfaces thereof are arranged in a straight line so that the respective beams B R , B G and B B emitted therefrom are directed in a substantially horizontal plane containing the axis of the gun, with the central beam B G being coincident with such axis. A first grid G 1 is spaced from the beam-generating surfaces of cathodes K R , K G and K B and has apertures g 1R , g 1G and g 1B formed therein in alignment with the respective cathode beam-generating surfaces. A common grid G 2 is spaced from the first grid G 1 and has apertures g 2R , g 2G and g 2B formed therein in alignment with the respective apertures of the first grid G 1 . Successively arranged in the axial direction away from the common grid G 2 are open-ended, tubular grids or electrodes G 3 , G 4 and G 5 , respectively, with cathodes K R , K G and K B , grids G 1 and G 2 , and electrodes G 3 , G 4 and G 5 being maintained in the depicted assembled positions thereof, by suitable, nonillustrated support means of an insulating material.

Screen S provided with the usual arrays of color phosphors S R , S G and S B and with an aperture grill G P or beam-selecting means, such as a so-called shadow mask. Disposed within the neck is a single electron gun A having cathodes K R , K G and K B , each of which is constituted by a beam-generating source with the respective beam-generating surfaces thereof disposed as shown in a plane which is substantially perpendicular to the axis of the electron gun. In the embodiment shown, the beam-generating surfaces thereof are arranged in a straight line so that the respective beams B R , B G and B B emitted therefrom are directed in a substantially horizontal plane containing the axis of the gun, with the central beam B G being coincident with such axis. A first grid G 1 is spaced from the beam-generating surfaces of cathodes K R , K G and K B and has apertures g 1R , g 1G and g 1B formed therein in alignment with the respective cathode beam-generating surfaces. A common grid G 2 is spaced from the first grid G 1 and has apertures g 2R , g 2G and g 2B formed therein in alignment with the respective apertures of the first grid G 1 . Successively arranged in the axial direction away from the common grid G 2 are open-ended, tubular grids or electrodes G 3 , G 4 and G 5 , respectively, with cathodes K R , K G and K B , grids G 1 and G 2 , and electrodes G 3 , G 4 and G 5 being maintained in the depicted assembled positions thereof, by suitable, nonillustrated support means of an insulating material.For operation of the electron gun of FIG. 1, appropriate voltages are applied to the grids G 1 and G 2 and to the electrodes G 3 , G 4 and G 5 . Thus, for example, a voltage of 0 to minus 400 v. is applied to the grid G 1 , a voltage of 0 to 500 v. is applied to the grid G 2 , a voltage of 13 to 20 kv. is applied to the electrodes G 3 and G 5 , and a voltage of 0 to 400v. is applied to the electrode G 4 , with all of these voltages being based upon the cathode voltage as a reference. As a result, the voltage distributions between the respective electrodes and cathodes, and the respective lengths and diameters thereof, may be substantially identical with those of a unipotential single beam-type electron gun which is constituted by a single cathode and first and second, single-apertured grids.

With the applied voltage distribution as described hereinabove, an electron lens field will be established between grid G 2 and the electrode G 3 to form an auxiliary lens L' as indicated in dashed line, and an electron lens field will be established around the axis of the electrode G 4 , by the electrodes G 3 , G 4 and G 5 , to form a main lens L, again as indicated in dashed lines.

Further included in the electron gun of FIG. 1 are electron be

am convergence deflecting means F which comprise shielding plates P and P' disposed in the depicted spaced, relationship at opposite sides of the gun axis, and axially extending, deflector plates Q and Q' which are disposed, as shown, in outwardly spaced, opposed relationship to shielding plates P and P', respectively. Although depicted as substantially straight, it is to be understood that the deflector plates Q and Q' may, alternatively, be somewhat curved or outwardly bowed, as is well known in the art.

am convergence deflecting means F which comprise shielding plates P and P' disposed in the depicted spaced, relationship at opposite sides of the gun axis, and axially extending, deflector plates Q and Q' which are disposed, as shown, in outwardly spaced, opposed relationship to shielding plates P and P', respectively. Although depicted as substantially straight, it is to be understood that the deflector plates Q and Q' may, alternatively, be somewhat curved or outwardly bowed, as is well known in the art.The shielding plates P and P' are equally charged and disposed so that the central electron beam B G will pass substantially undeflected between the shielding plates P and P', while the deflector plates Q and Q' have negative charges with respect to the plates P and P' so that respective electron beams B B and B R will be convergently deflected as shown by the respective passages thereof between the plates P and Q and the plates P' and Q'. More specifically, a voltage V P which is equal to the voltage applied to the electrodes G 3 and G 5 , may be applied to both shielding plates P and P', and a voltage V Q , which is some 200 to 300 v. lower than the voltage V P , is applied to the respective deflector plates Q and Q' to

result in the respective shielding plates P and P' being at the same potential, and to result in the application of a deflecting voltage difference or static convergence deflecting voltages V C between the respective plates P' and Q' and P and Q and it is, of course, this convergence-deflecting voltage V C which will impart the requisite convergent deflection to the respective electron beams B B and B R .

result in the respective shielding plates P and P' being at the same potential, and to result in the application of a deflecting voltage difference or static convergence deflecting voltages V C between the respective plates P' and Q' and P and Q and it is, of course, this convergence-deflecting voltage V C which will impart the requisite convergent deflection to the respective electron beams B B and B R .In operation, the respective electron beams B R , B G and B B which emanate from the beam-generating surfaces of the cathodes K R , K G and K B will pass through the respective grid apertures g 1R , g 1G and g 1B , to be intensity modulated with what may be termed the "red", "green" and "blue" intensity modulation signals applied between the said cathodes and the first grid G 1 . The respective electron beams will then pass through the common auxiliary lens L' to cross each other substantially at the optical center of the main lens L and to emerge from the latter with beams B R and B B diverging from beam B G . Thereafter, the central electron beam B G will pass substantially undeflected between shielding plates P and P' since the latter are at the same potential. Passage of the electron beam B B between the plates P' and Q' and of the electron beam B R between the plates P and Q will, however, result in the convergent deflections thereof as a result of the convergence-deflecting voltage applied therebetween, and the system of FIG. 1 is so arranged that the electron beams B B , B G and B R will desirably converge or cross each other at a common spot centered in an aperture of the aperture grill G P or other beam selecting means so as to diverge therefrom to strike the respective color phosphors of a corresponding array thereof on screen S. More specifically, it may be noted that the color phosphor screen S is composed of a large plurality of sets or arrays of vertically extending "red", "green" and "blue" phosphor stripes or dots S R , S G and S B with each of the arrays or sets of color phosphors forming a color picture element. Thus, it will be understood that the common spot of beam convergence corresponds to one of the thusly formed color picture elements.

The voltage V P applied to the lens electrodes G 3 and G 5 and to plates P and P', is also applied to the screen S as an anode voltage in conventional manner through a nonillustrated graphite layer which is provided on the inner surface of the cone of the tube envelope. Thus, to summarize the operation of the depicted color picture tube of FIG. 1, the respective electron beams B B , B G and B R will be converged at aperture grill G P and will diverge therefrom in such manner that electron beam B B will strike the "blue" phosphor S B , electron beam B G will strike the "green" phosphor S G and electron beam B R will strike the "red" phosphor S R of the array or set corresponding to the aperture at which the beams converge. Electron beam scanning of the face of the color phosphor screen is effected by horizontal and vertical deflection yoke means which receives horizontal and vertical sweep signals whereby a color picture will be provided on the color screen. Since, with this arrangement, the respective electron beams are each passed, for focusing, through the center of the main lens L of the electron gun A, the beam spot formed by impingement of the beams on the color phosphor screen S will be substantially free from the effects of coma and/or aberration of the said main lens, whereby improved color picture resolution will be provided.

The horizontal deflection current-generating circuit indicated generally at 21 is shown to include a horizontal power transistor 22 connected, at its base, to a terminal 22' receiving a horizontal driving pulse from the usual horizontal deflection driving circuit (not shown), a damper diode 23, a flyback transformer 25, the horizontal deflecting coil 26 of the previously mentioned deflection yoke means, and a capacitor 27. The primary winding 25 a of transformer 25 is shown connected between a terminal 24 receiving power from a suitable source (not shown) and the collector of transistor 22 having its emitter connected to ground, and the damper diode 23 is connected between primary winding 25a and ground in parallel with transistor 22. The horizontal deflecting coil 26 and the capacitor 27 are connected in series between winding 25a and ground, that is, in parallel with diode 23.

The flyback transformer 25 is shown to have a secondary winding 25b connected to a high voltage-generating means 28 receiving pulses from winding 25b in synchronism with the horizontal driving pulse supplied to te

rminal 22', and the high voltage-generating means 28 includes a rectifier 28a to produce, from the received pulses, a constant high voltage V P which appears between output terminal 29 and ground. This high voltage V P is, as described above, applied to an anode of the picture tube, the electrodes G 3 and G 5 and also the convergence-deflecting plates P and P' by way of a terminal 33.

rminal 22', and the high voltage-generating means 28 includes a rectifier 28a to produce, from the received pulses, a constant high voltage V P which appears between output terminal 29 and ground. This high voltage V P is, as described above, applied to an anode of the picture tube, the electrodes G 3 and G 5 and also the convergence-deflecting plates P and P' by way of a terminal 33.A resistor 30, the secondary winding 31b of an isolating transformer 31 and a variable resistor 32 are connected in series between the output terminal 29 and the ground so that the high voltage V P is divided by resistors 30 and 32 into the static convergence voltage V C and the voltage V Q , with the voltage V C appearing across resistor 30 and being easily adjustable by means of the variable resistor 32. Further, capacitors 44 and 45 are connected in parallel with resistors 30 and 32 for stabilizing the voltages V C and V Q .

The flyback transformer 25 is further shown to include an additional secondary winding 25c across which an inductance 35 and the resistance of a potentiometer 36 are connected in series to function as an integration circuit 37. Series connected capacitors 38 and 39 are connected between ground and the connection point between capacitor 27 and the horizontal deflection coil 26, that is, capacitors 38 and 39 are connected in parallel with capacitor 27, and the connecting point between capacitors 38 and 39 is connected to a middle tap 40 provided on the resistance of potentiometer 36. The connecting point 41 between capacitors 27 and 38 is connected to one end of the primary winding 31a of isolating transformer 31 through a variable inductor 43, and the other end of winding 31a is connected to the output terminal 42 of potentiometer 36 from which there extends the slider or movable tap 42'. The variable inductor 43 is p

rovided to permit adjustment of the voltage developed at connecting point 41. Finally, a terminal 34 extending from the connecting point between winding 31b of the isolating transformer and variable resistor 32 is connected to plates Q and Q'.

rovided to permit adjustment of the voltage developed at connecting point 41. Finally, a terminal 34 extending from the connecting point between winding 31b of the isolating transformer and variable resistor 32 is connected to plates Q and Q'.The above-described circuits operate as follows:

The pulse voltage developed across winding 25c, and which is synchronized with the horizontal scan period, is converted into a voltage of sawtooth wave configuration by the series connected inductor 35 and the resistance of potentiometer 36, and such voltage of sawtooth wave configuration appears across the resistance of potentiometer 36. Simultaneously, a horizontal deflecting current of sawtooth wave configuration flows through horizontal deflecting coil 26 and the capacitor 27 in series therewith, with the result that a voltage of a parabolic waveform is developed across capacitor 27, that is, between connecting point 41 and ground. This voltage of parabolic waveform is divided b

y capacitors 38 and 39 so that a voltage of parabolic waveform is developed across capacitor 38, as indicated at 46 on FIG. 2B. The voltage 46 of parabolic waveform is applied to primary winding 31a of isolating transformer 31 through the adjusting inductor 43. The voltage of sawtooth wave configuration appearing across the resistance of potentiometer 36 developes a voltage at the output terminal 42 of the latter in dependence on the position of slider 42' and such voltage at terminal 42 is also applied to primary winding 31a of the isolating transformer. Thus, if slider 42' is at a midposition on the resistance of potentiometer 36, no voltage is developed at terminal 42 as represented by the line 47 on FIG. 2C. However, if slider 42' is displaced in one direction or the other from such midposition, a corresponding voltage of sawtooth configuration is developed at terminal 42, for example, as indicated at 48 or 49 on FIG. 2C, and such sawtooth voltage 48 or 49 is also applied to winding 31a. Therefore, the voltage applied to primary winding 31a of the isolating transformer is a combination of the parabolic voltage 46 and the sawtooth voltage 48 or 49, if any, appearing at terminal 42. Thus, there is produced, across the secondary winding 31b, a horizontal dynamic convergence deflecting voltage e c which is either parabolic, as at 51 on FIG. 2D, in the case when there is no voltage developed at terminal 42 as represented at 47 on FIG. 2C, or which is the resultant of parabolic and sawtooth wave forms, as indicated at 52 or 53 on FIG. 2D when the sawtooth voltage 48 or 49, respectively, of FIG. 2C is applied to winding 31a.

y capacitors 38 and 39 so that a voltage of parabolic waveform is developed across capacitor 38, as indicated at 46 on FIG. 2B. The voltage 46 of parabolic waveform is applied to primary winding 31a of isolating transformer 31 through the adjusting inductor 43. The voltage of sawtooth wave configuration appearing across the resistance of potentiometer 36 developes a voltage at the output terminal 42 of the latter in dependence on the position of slider 42' and such voltage at terminal 42 is also applied to primary winding 31a of the isolating transformer. Thus, if slider 42' is at a midposition on the resistance of potentiometer 36, no voltage is developed at terminal 42 as represented by the line 47 on FIG. 2C. However, if slider 42' is displaced in one direction or the other from such midposition, a corresponding voltage of sawtooth configuration is developed at terminal 42, for example, as indicated at 48 or 49 on FIG. 2C, and such sawtooth voltage 48 or 49 is also applied to winding 31a. Therefore, the voltage applied to primary winding 31a of the isolating transformer is a combination of the parabolic voltage 46 and the sawtooth voltage 48 or 49, if any, appearing at terminal 42. Thus, there is produced, across the secondary winding 31b, a horizontal dynamic convergence deflecting voltage e c which is either parabolic, as at 51 on FIG. 2D, in the case when there is no voltage developed at terminal 42 as represented at 47 on FIG. 2C, or which is the resultant of parabolic and sawtooth wave forms, as indicated at 52 or 53 on FIG. 2D when the sawtooth voltage 48 or 49, respectively, of FIG. 2C is applied to winding 31a.As a result of the foregoing, the convergence-deflecting voltage V C +e c , as indicated at 54, 55 or 56 on FIG. 2E and which respectively consists of the static convergence voltage V C of FIG. 2A superimposed upon the horizontal dynamic convergence voltage e c shown at 51, 52 or 53, respectively, of FIG. 2D, is developed across terminals 33 and 34 and, hence, applied between plates P and Q and plates P' and Q'. It will be apparent that, in the described arrangement according to this invention, the magnitude of the static convergence voltage V C is easily controllable by the variable resistor 32 and that the wave shape and magnitude of the horizontal dynamic convergence voltage e c are also easily controllable by the potentiometer 36 and the variable inductor 43 which are at the primary winding side of isolating transformer 31. Further, such adjustments for insuring proper convergence of the beams can be effected without coming into contact with any high-voltage portion of the circuits.

It will also be seen that, since the static convergence-deflecting voltage V C is produced by dividing the anode voltage V P in accordance with the ratio of resistors 30 and 32, which ratio remains constant in the absence of adjustment of resistor 32, the voltage V C will be varied in accordance with variations in the anode voltage V P . Thus, if, for example, the anode voltage V P decreases with an increase in the anode current, the voltage V C will correspondingly decrease to maintain the ratio V C /V P at a constant value so as to maintain the proper convergence of the beams.

Referring now to FIG. 3, it will be seen that the circuit arrangement there shown is generally similar to that of FIG. 1 and has its several components identified by the same reference numerals. However, in the circuit of FIG. 3, the secondary winding 31b of isolating transformer 31 is not connected in series between resistors 30 and 32, but rather has one end connected to the connecting point 57 between those resistors and its other end connected to terminal 34. Thus, the static convergence-deflecting voltage V C is produced across resistor 30, that is, between terminal 33 and connecting point 57, and the horizontal dynamic convergence-deflecting voltage e c is produced across winding 31b, that is, between connecting point 57 and terminal 34, with the result that the combined convergence-deflecting voltage V C +e c again appears between terminals 33 and 34. As in the first described embodiment, terminal 33 is connected to the electrodes G 3 and G 5 , the anode and the plates P and P' of the tube (not shown), while the terminal 34 is connected to the plates Q and Q' of the tube.

Referring now to FIG. 3, it will be seen that the circuit arrangement there shown is generally similar to that of FIG. 1 and has its several components identified by the same reference numerals. However, in the circuit of FIG. 3, the secondary winding 31b of isolating transformer 31 is not connected in series between resistors 30 and 32, but rather has one end connected to the connecting point 57 between those resistors and its other end connected to terminal 34. Thus, the static convergence-deflecting voltage V C is produced across resistor 30, that is, between terminal 33 and connecting point 57, and the horizontal dynamic convergence-deflecting voltage e c is produced across winding 31b, that is, between connecting point 57 and terminal 34, with the result that the combined convergence-deflecting voltage V C +e c again appears between terminals 33 and 34. As in the first described embodiment, terminal 33 is connected to the electrodes G 3 and G 5 , the anode and the plates P and P' of the tube (not shown), while the terminal 34 is connected to the plates Q and Q' of the tube.Although illustrative embodiments of the invention have been described in detail herein with reference to the accompanying drawings, it is to be understood that the invention is not limited to those precise embodiments, and that various changes and modifications may be effected therein by one skilled in the art without departing from the scope or spirit of the invention.

M58485P a 29-function remote control

DESCRIPTION

DESCRIPTIONThe M58485P is a 29-function remotecontrol receiver

circuit manufactured by aluminum-gate CMOS technology

for use in television receivers, audio equipment, and the

like using infrared for transmission. It enables direct con-

trol of 12 functions at the receiver.

The M58485P is intended for use with an M5848OP or

M58484P transmitter.

FEATURES

0 Single power supply

0 Wide supply voltage range: 8V~14V

0 Low power dissipation

0 On-chip oscillator

0 Low-cost LC or ceramic oscillator used in determining

reference frequency (480 kHz or 455 kHz)

0 Information is transmitted by pulse code modulation

0 Good noise immunity-instructions are not executed

unless the same code is received three or more times in

succession

° Single transmission frequency (40kHz or 38 kHz) for

carrier wave

0 16 TV channels selected directly

0 Three analog functions-volume, brightness, and color

saturation_are independently controlled to 64 stages

by three 6-bit D/A converters.

0 12 instructions are controlled at the M58485P reoeiver,

as well.

0 Has large tolerance in operating frequency between the

transmitter and the receiver

0 Can be connected with an M51231P or equivalent

touch-control channel selector

FUNCTION

The M58485P is designed to decode and execute instruc

tions after three successive receptions of the identica

instruction code, providing a good noise immunity.

Instructions comprise direction selection of 16 channels

channel position high and low, volume high and low, brigh1

ness high and low, color saturation high and low, normalize

tion of volume, brightness and color saturation, sound mut~

on and off, TV main power on and off, and output CALI

on and off.

In addition, 12 functional instructions can be enteree

from the receiver.

Indication of Reception

As soon as an identical code is received three times, the

output IR turns from low-level to high-level. Thus reception

of a command from the transmitter can be indicated by an

LED connected to output IR.

Analog Outputs (CO. BR, CS)

As three 6-bit D/A converters are contained internally,

three kinds of analog values can be controlled to 64 stages

independently. The D/A converters are pulse-width modula-

tor, and the repetition frequency is 1.25 kHz (when f°s¢=

480 kHz) and minimum pulse width is l2.5us.

Analog values can be incremented/decremented at a rate

of about 1 step/0.1 sec through the remote control or the

key input. The time required for increasing the analog value

from the minimum to the maximum is about 6.6 seconds

(When f0SC=480

It is also possible to set the analog values to 1/3 (VO),

1/2 (BR, CS) of these maximum values by means of the

remote control or the key input (normalization).

Sound Mute

Sound mute on/off is controlled through the remote con-

trol or the key input. When sound mute is on, output VO

goes low, and output MUTE goes high.

Sound mute is automatically released from ON when VO

is either incremented or decremented by remote control

or the key input.

Channel Control

It is possible to employ either of two channel control

methods: parallel control by outputs P0~P3, and serial

control by outputs CWLF, , and .

In parallel control, a 4-bit address corresponding to a

selected channel number appears at output P0~P3. Table 3

shows the relations between channel numbers and outputs

P0~P3.

In serial control, a single pulse appears on the output

( first, and then the pulses whose number is

deducted by one from the selected channel number appear

on the output @W, as shown in Fig. 6. Up and down

channel switching is controlled by a single pulse appearing

at output (flwor , allowing connection to the

M51231P or equivalent touch-control channel selector IC.

Power on/off

The remote control or the key input makes it possible to

turn the POWER ON/OFF output from low to high or vice

versa, and it is possible to change the POWER ON/OFF

output from low to high by means of the POWER ON

input.

While POWER ON/OFF is low, all channel and analog

controls through the remote control are disabled, as are all

through the keyboard.

Output CALL

The output CALL is turned high or low by remote control

or the key input. This output effects on/off control of

channel number indication or change of receiving modes

of multi-channel broadcasting.

Power-on Reset

Attaching a capacitor to terminal AC activates the power-

on reset function when power is on to the M58485P.

Activation of the power-on reset function sets outputs

VO, BR, and CS to 1/3, 1/2, and 1/2, respectively, of their

maximum value, turns POWER ON/OFF and CALL outputs

low and turns outputs P0»-P3 to 0000.

SONY KV-2204ET CHASSIS SCC-216B-A Digitally controlled tuner with automatic fine tuning:

A tuning system for digitally controlled electronically tuned tuner with automatic fine tuning (AFT) constantly operable to hold the tuner at a predetermined optimum frequency setting, especially a television channel. A reversible counter provides the digital signal to control the tuning of the tuner and is, itself, deliberately shifted from one setting to another by pulses from a source, such pulses being applied to the UP input terminal of the counter as the up-tuning pulses to shift the tuner frequency higher. Pulses from the same source are also used as down-tuning pulses when applied to the DOWN input terminal of the tuning pulses to a lower frequency supplied to two AFT AND circuits. One output logic up-tuning instruction signal EU of the AFT circuit enables the up-tuning AFT AND circuit only in a certain sub-range below the desired frequency. The other output logic down-tuning instruction signal ED of the AFT circuit enables the other AFT AND circuit only in a certain sub-range above the desired frequency. Consequently, deliberate application of up-or-down-tuning pulses to the UP or DOWN terminals changes the count as desired, being only partially counteracted by the lower frequency, AFT-controlled pulses to the opposite counter terminal.

1. A channel selecting apparatus comprising an electronically tuned tuner, a reversible counter having an UP input terminal and a DOWN input terminal to receive pulses to cause said counter to count UP and DOWN, respectively, digital-to-analog converter means connected to said counter to receive digital count from the latter and to convert the same to an analog signal to control the tuning of said tuner, an automatic fine tuning circuit comprising means to generate automatic fine tuning control signals when said tuner is tuned within an automatic fine tuning range centered about a channel frequency, said signals including an up-tuning control signal when said tuner is tuned within said range but below the channel frequency in that range and a down-tuning control signal when said tuner is tuned within said range between the channel frequency in that range and an upper frequency of that range, a source of first pulses having a predetermined frequency, first connection means for selectively channeling said first pulses to said UP and DOWN input terminals of said counter for bringing said tuner from one channel to another, a source of second pulses having a frequency lower than that of said first pulses, and second connection means for selectively channeling said second pulses to said UP and DOWN input terminals, said automatic fine tuning circuit being connected to said second connection means to cause said second connection means to transmit said second pulses to said UP input terminal in response to said up-tuning control signal and to transmit said second pulses to said DOWN input terminal in response to said down-tuning control signal.

2. The channel selecting apparatus of claim 1 in which said first connection means comprises:

first and second AND circuits both connected to receive said first pulses from said source thereof, said first AND circuit being connected to said UP input terminal and said second AND circuit being connected to said DOWN input terminal; and

selective means to enable either of said AND circuits to allow the passage therethrough of said first pulses to the respective UP or DOWN input terminal.

3. The channel selecting apparatus of claim 2 in which said selective means comprises switch means to apply, selectively, a "1" signal to said first or said second AND circuit to enable that selected AND circuit to pass said first pulses to the respective UP or DOWN input terminal.

4. The channel selecting apparatus of claim 1 in which said means to produce said second pulses comprises a frequency divider connected to said source of said first pulses to divide the frequency of said first pulses to that of said second pulses.

5. The channel selecting apparatus of claim 4 in which said frequency divider is a divide-by-two frequency divider.

6. The channel selecting apparatus of claim 1 comprising first and second AND circuits both connected to said means to produce second pulses, said first AND circuit being connected to a terminal of said fine tuning circuit to receive said up-tuning control signal therefrom and said second AND circuit being connected to a second output terminal of said fine tuning circuit to receive said down-tuning control signal therefrom, said first AND circuit being connected to said UP input terminal to supply said second pulses thereto when said up-tuning control signal has a logic value of "1", and said second AND circuit being connected to said DOWN input terminal to supply said second pulses thereto when said down-tuning control signal has a logic value of "1".

7. The channel selecting apparatus of claim 6 comprising third and fourth AND circuits both connected to said source of first pulses;

first actuation means connected to said third AND circuit to apply a signal having a logic value of "1" to said third AND circuit, selectively, to allow said third AND circuit to conduct said first pulses therethrough;

second actuation means connected to said fourth AND circuit to supply selectively a signal having a logic value of "1" to make said fourth AND circuit conductive to said first pulses;

a first OR circuit having an output terminal connected to said UP input terminal of said counter and having input terminals connected to output terminals of said first and third AND circuits to transmit to said UP input terminal either said first pulses or said second pulses;

a second OR circuit having an output terminal connected to said DOWN input terminal of said counter and having input terminals connected to output terminals of said second and fourth AND circuits to supply to said DOWN input terminal said first or second pulses, the transmission of said first pulses through said third and fourth AND circuits being

determined by said first and second actuation means, respectively and alternately, and the transmission of said second pulses through said first and second AND circuits being controlled by said up-tuning and down-tuning control signals, respectively, of said automatic fine tuning circuit independently of said actuation means.

determined by said first and second actuation means, respectively and alternately, and the transmission of said second pulses through said first and second AND circuits being controlled by said up-tuning and down-tuning control signals, respectively, of said automatic fine tuning circuit independently of said actuation means.The invention described hereinafter is related to the inventions described in the following U.S. applications:

U.S. Patent application Ser. No. 716,655, filed Aug. 23, 1976, now U.S. Pat. No. 4,085,371, issued Apr. 18, 1978;

U.S. Patent application Ser. No. 716,702, filed Aug. 23, 1976, now U.S. Pat. No. 4,085,372, issued Apr. 18, 1978;

U.S. Patent application Ser. No. 716,654, filed Aug. 23, 1976;

U.S. Patent application Ser. No. 717,477, filed Aug. 25, 1976, now U.S. Pat. No. 4,058,772, issued Nov. 15, 1977;

U.S. Patent application Ser. No. 740,753, filed Nov. 10, 1976;

U.S. Patent application Ser. No. 743,008, filed Nov. 18, 1976, now U.S. Pat. No. 4,079,420, issued Mar. 14, 1978;

U.S. Patent application Ser. No. 743,523, filed Nov. 19, 1976, now U.S. Pat. No. 4,079,320, issued Mar. 14, 1978.

Field of the Invention

This invention relates to a digitally controlled, electronic tuner that can be tuned to any of several different channels at different frequencies and which includes an automatic fine tuning (AFT) circuit to adjust the tuning precisely when the frequency to which the tuner is tuned is within a predetermined frequency range close to the exact desired frequency. In particular, the invention relates to a television signal tuner for a receiver having an AFT circuit to maintain the tuning at a selected frequency according to one of the available channels and further including means to overcome the effect of the AFT circuit when it is desired to shift the tuner to a different channel.

U.S. Pat. No. 4,085,371 describes a television receiver tuner in which the basic tuning is accomplished by controlling the voltage on the one or more varactors in the circuits to be tuned. Varactors are capacitors, the capacitance of which is determined by the magnitude of the direct voltage applied across the capacitor terminals. The tuning circuit includes a memory section that retains information in digital form according to the frequencies to which the tuner may be set. Such information may be generated in the overall circuit and applied to the memory section by a user of the television receiver, normally at the time the set is first placed in operation. Television channels are commonly identified by number and there are usually not more than a dozen or so channels at any one location. Thus a receiving set incorporating the electronic tuner of the aforesaid Pat. No. 4,085,371 is likely to be adjusted to receive each of the available channels in turn when the set is first placed in use. Thereafter tuning is simply accomplished by actuating a switch according to the desired channel.

However, because of aging factors in the circuit or environmental factors that affect the receiver, the initial tuning information stored in digital form may become incorrect after the lapse of an indeterminate time. If the memory section always instructs the varactor control circuit to apply a certain voltage to the varactor or to the multiple varactors according to the initial setting memorized in the memory circuit, the receiver might eventually be tuned to a frequency different from the desired channel. The difference would become increasingly apparent as fuzziness of image or perhaps distortion of sound. Accordingly, the aforesaid U.S. Pat. No. 4,085,371 defines an AFT circuit that begins to operate when the frequency to which the tuner is set is within a certain range of the exact frequency for a channel. The range may be, for example ±1.2 MHz. This range is further divided into a sub-range just above the exact desired frequency and extending out to +1.2MHz above the desired frequency and another sub-range that extends from the desired frequency to a frequency lower by 1.2 MHz. If the tuner is operating so that the carrier of the received signal falls within the upper sub-range, the AFT circuit applies pulse signals to adjust the tuning downwardly to the desired frequency. Conversely, if the carrier of the received signal is in the lower sub-range, a different signal is applied from the AFT circuit to shift the tuning upwardly to the desired frequency.

While the tuner has been referred to as being "set" at a frequency, that is somewhat incorrect; it is to be understood that the setting may be changing virtually continuously as the tuner is adjusted from one desired frequency to another. For example, if the tuner is set to receive channel 2 and the user decides to switch to channel 5, the tuner will be required to leave the proper setting for channel 2, pass through the upper sub-range of that channel, and pass through the lower and upper sub-ranges associated with channels 3 and 4 in succession in order to reach the lower sub-range and then the desired precise frequency of channel 5. The effect of the AFT circuit must be overcome in order to keep the voltage produced by the AFT circuit from locking the tuner at the frequency of channel 2 or the frequencies of channels 3 and 4.

It is a principal object of the present invention to provide a digital tuner having a control circuit that will, at all times, be capable of supplying an AFT control signal to effect both upward and downward tuning within a certain range of frequencies adjacent received frequencies, the control circuit further including means to supply signals to overcome the effect of the AFT signal.

It is a further object of the invention to generate the AFT control signal as pulses at a repetition rate lower than the repetition rate of the pulses supplied to effect deliberate shifting of the operating frequency of the tuner.

Further objects will become apparent from the following specification together with the related drawings.

In accordance with the present invention pulses are generated and are connected through a control circuit to a reference control counter to cause the counter either to count up or down. The digital output signal of the counter is applied to a digital-to-analog (D/A) converter that converts the digital count into an analog signal. This analog signal is applied to an electronic tuner to adjust voltage controlled means, such as one or more varactors therein, to determine the frequency to which the tuner is adjusted. This frequency may shift from instant to instant as the count in the counter changes either up or down.

An AFT circuit, which may include a frequency discriminator, is connected to the output of the tuner or to an intermediate frequency amplifier of the type that commonly follows the tuner in a cascade connection therewith. The AFT circuit is arranged to operate only within a certain band of frequencies. The center of this band is the carrier frequency of the signal applied to the AFT circuit. When the carrier of an incoming signal is in an upper sub-range above the center frequency of the discriminator, the AFT circuit generates a logic signal at the down-counting output terminal of the AFT circuit to effect downward tuning. When the carrier of the received signal at the input of the AFT circuit is in a lower sub-range below the desired frequency, the AFT circuit generates a logic signal at its up-counting output terminal to effect upward tuning of the electronic tuner.

The counter circuit is controlled by pulses received from a control circuit. These pulses may be applied either to the up-counting or the down-counting input circuit of the counter. Between the pulse generator and the up-counting and down-counting input terminals are two AND circuits, each connected in cascade with a respective OR circuit. The AND circuits are controlled, respectively, by logic signals which, in turn, are controlled by actuation of an up-counting or down-counting switch. The pulse signals applied from the pulse generator pass through one AND circuit to its associated OR circuit to the up-counting terminal when the switch to effect up-counting is actuated to enable that AND circuit. Conversely, signals from the pulse generator pass through the other AND circuit and its associated OR circuit to the down-counting terminal of the counter when the down-counting switch is actuated to enable the latter AND circuit.

Two other AND circuits have their output terminals connected to second input terminals of the aforementioned OR circuits, respectively. One of the latter AND circuits is connected to the down-counting output terminal of the AFT circuit to receive the logic signal therefrom to enable that AND circuit when the input signal to the AFT circuit is in the upper sub-range. Conversely, the other of the latter two AND circuits has an input terminal connected to the up-counting output terminal of the AFT circuit to be enabled by the logic signal therefrom when the frequency of the signal applied to the input of the AFT circuit is in the lower sub-range.

The other input terminal of the latter two AND circuits is connected to receive pulses from the pulse generator. However, in accordance with this invention, between the pulse generator and the latter two AND circuits is a frequency divider so that the pulses applied to the latter two AND circuits are at a sub-multiple frequency of the signals applied to the first two AND circuits. As a result, although the AFT circuit is constantly operating and supplies either an up-counting logic signal or a down-counting logic signal when the signal applied to its input is in the appropriate range, the resulting AFT pulses that attempt to bring the counter to a specific count value or to hold it at that count value will not be able to do so because the pulses that reach the counter by deliberate actuation of either the up-counting control switch or the down-counting control switch have a higher frequency that changes the count of the counter faster than the count can be pulled back to a previous condition.

FIG. 1 is a block diagram illustrating a channel selecting apparatus with AFT.

FIG. 2 is a block diagram illustrating, in greater detail, an up-down counter for generating channel identifying codes and a memory which are included in the apparatus of FIG. 1.

FIG. 3 is a detail block diagram of a pulse-width modulator which is included in the apparatus shown in FIG. 1.

FIGS. 4A-4E are waveform diagrams to which reference will be made in explaining the operation of the channel selecting apparatus of FIG. 1.

FIG. 5 is a schematic circuit diagram showing a portion of an automatic fine tuning circuit that is included in the apparatus according to this invention.

FIGS. 6A-6C and FIGS. 7A-7I are waveform diagrams to which reference will be made in explaining the automatic fine tuning operation of the channel selecting apparatus according to this invention.

FIG. 8 is a block diagram illustrating channel selecting apparatus according to this invention to overcome the effect of AFT when deliberately tuning from one channel to another.

FIGS. 9A and 9B are waveform diagrams illustrating AFT logic signals for effecting up-tuning and down-tuning, respectively.

FIG. 1 is a block diagram of a channel selecting circuit as claimed in the aforesaid companion case Ser. No. 716,654 but will be described here as an especially useful introduction to the present invention. It comprises a generator 10 of a clock pulse A o which is applied to a timing counter 20 for producing a circulating digital, or binary, code A 1 , A 2 , A 3 ---A 14 . A manually controllable sweep pulse generating circuit 30 is provided to produce either up-tuning pulses P U or down-tuning pulses P D to corresponding terminals of an up-down counter 40. In the programming mode of the apparatus, the counter 40 counts the pulses P U or P D to establish channel identification digital codes B 1 , B 2 , B 3 ---B 14 corresponding to the changing counts of the counter 40. These codes are recorded, or stored, at selected addresses in a memory 50.

FIG. 1 is a block diagram of a channel selecting circuit as claimed in the aforesaid companion case Ser. No. 716,654 but will be described here as an especially useful introduction to the present invention. It comprises a generator 10 of a clock pulse A o which is applied to a timing counter 20 for producing a circulating digital, or binary, code A 1 , A 2 , A 3 ---A 14 . A manually controllable sweep pulse generating circuit 30 is provided to produce either up-tuning pulses P U or down-tuning pulses P D to corresponding terminals of an up-down counter 40. In the programming mode of the apparatus, the counter 40 counts the pulses P U or P D to establish channel identification digital codes B 1 , B 2 , B 3 ---B 14 corresponding to the changing counts of the counter 40. These codes are recorded, or stored, at selected addresses in a memory 50. Further, the channel selecting apparatus shown in FIG. 1 generally comprises a memory control circuit 60 for selectively establishing the programming mode of operation or a channel selecting mode of operation in which a channel identification digital code previously stored at a selected address in memory 50 is read out therefrom, as indicated at C 1 , C 2 , C 3 ---C 14 , and applied to counter 40 to establish the corresponding count in the latter. A manually controllable address selecting circuit 70 is provided for activating a selected address in the memory 50 for either recording a selected channel identification code or reading out a previously stored channel identification code from that address during the programming or channel selecting modes, respectively. A band-indicating signal-forming circuit 80 which, in the programming mode of operation, produces a signal indicating the band of the channel indicating code then being stored at a selected address of memory 50, with such band indicating signal also being stored at the respective address.

The channel selecting apparatus shown in FIG. 1 also generally comprises a D/A converter 90 that provides an analog control voltage for the varactor of a selected band in an electronic tuner 100. The analog control voltage corresponds to the count of the counter 40 as established by a channel identification digital code selectively read out of the memory 50 in the channel selecting mode of the apparatus. In the programming mode the analog voltage corresponds to the changing counts produced by the counter 40 when the latter counts tuning pulses from the generating circuit 30. A video intermediate frequency amplifier 110 receives the output of the tuner 100 and has its own output applied to a conventional video detector circuit as in the usual color television receiver.

The channel selecting apparatus shown in FIG. 1 also generally comprises a D/A converter 90 that provides an analog control voltage for the varactor of a selected band in an electronic tuner 100. The analog control voltage corresponds to the count of the counter 40 as established by a channel identification digital code selectively read out of the memory 50 in the channel selecting mode of the apparatus. In the programming mode the analog voltage corresponds to the changing counts produced by the counter 40 when the latter counts tuning pulses from the generating circuit 30. A video intermediate frequency amplifier 110 receives the output of the tuner 100 and has its own output applied to a conventional video detector circuit as in the usual color television receiver. The output of the video intermediate frequency amplifier 110 is also applied to an automatic fine tuning (AFT) circuit 120 which includes a frequency discriminator that responds to a video carrier wave in the output of the IF amplifier 110 to produce AFT logic signals from up-counting and down-counting outputs E U and E D . These logic signals are produced when the channel identification code then being applied to the converter 90 for establishing a receiving frequency in the channel selecting mode of the apparatus has to be modified upwardly or downwardly, respectively, for attaining precisely the correct receiving frequency for the respective channel. The discriminated outputs E U and E D are applied to the sweep pulse generating circuit 30. As will be hereinafter described in detail, the circuit 30 responds to the discriminated output E U or E D to provide tuning pulses to be counted by the counter 40 for modifying the channel identifying code applied therefrom to the converter 90 to obtain precisely the correct receiving frequency, that is, for achieving the desired AFT operation.

Further, a memory rewriting circuit 130 is provided in the channel selecting apparatus. As will be hereinafter described in detail, when the extent to which the channel identification code being read out of a selected address in the memory 50 to the counter 40 has to be modified to obtain the correct receiving frequency for the respective channel exceeds a predetermined amount, the rewriting circuit causes the writing of the modified channel identifying code at the selected address in place of the code originally stored thereat. In this way, the memory rewriting circuit 130 ensures that the channel identification codes stored in the memory 50 will not, in time, result in respective receiving frequencies that are outside the pull-in range of the AFT operation. Finally, the channel selecting apparatus comprises an AFT inhibit circuit 140 which is effective, as will be hereinafter described in detail, to prevent the AFT operation during the initial application of power to the apparatus and during operation of the address selecting circuit 70.

In the channel selecting apparatus as generally described above, the clock pulse A o from the generator 10 may have a frequency of, for example, 4 MHz resulting in a period τ of 0.25 μsec. In the timing counter 20, the clock pulse A o is counted to produce pulses A 1 , A 2 , A 3 ---A 14 which are frequency-divided in sequence so as to range from pulses A 1 that have a period of 0.5 μsec. and a pulse width of 0.25 μsec., to pulses A 14 that have a period of 4.096 m.sec. and a pulse width of 2.048 m.sec. The pulses A 1 , A 2 , A 3 ---A 14 form a 14-bit circulating digital code which changes its state 2 14 times, that is, 16,384 times, within the circulating or repeating period of T = 2 14 τ = 4.096 m. sec. (FIGS. 4A and B).

In the pulse generating circuit 30 as shown in FIG. 1, a fine up-tuning switch 31FU, a fine down-tuning switch 31FD, a coarse up-tuning switch 31CU and a coarse down-tuning switch 31CD are connected in series with respective resistors 32 1 , 32 2 , 32 3 and 32 4 , and such series circuits are connected in parallel between a voltage source +5V and ground. The switches 31FU, 31FD, 31CU and 31CD are normally open, as shown, to provide logic signals at the high logic level "1" at the junctions of such switches with the respective resistors 32 1 , 32 2 , 32 3 and 32 4 and the input terminals of inverters 33 1 , 33 2 , 33 3 and 33 4 . When any of the switches 31FU, 31FD, 31CU and 31CD are closed, a logic signal at the low logic level "0" is applied to the input terminals of the respective inverters 33 1 , 33 2 , 33 3 and 33 4 . The "1" or "0" logic controlled by the switches 31FU, 31FD, 31CU and 31DC are inverted by the corresponding inverters to first input terminals of NAND circuits 34 1 , 34 2 , 34 3 and 34 4 , respectively. The pulses A 14 having a period of 4.096 m. sec. are applied from the timing counter 20, as coarse tuning pulses, to second inputs of the NAND circuits 34 3 and 34 4 . The pulses A 14 are also applied to a frequency divider 35 to be divided, for example, by 64, to provide fine tuning pulses having a period of 262.144 m. sec., and such fine tuning pulses are applied to second inputs of the NAND circuits 34 1 and 34 2 .

In the pulse generating circuit 30 as shown in FIG. 1, a fine up-tuning switch 31FU, a fine down-tuning switch 31FD, a coarse up-tuning switch 31CU and a coarse down-tuning switch 31CD are connected in series with respective resistors 32 1 , 32 2 , 32 3 and 32 4 , and such series circuits are connected in parallel between a voltage source +5V and ground. The switches 31FU, 31FD, 31CU and 31CD are normally open, as shown, to provide logic signals at the high logic level "1" at the junctions of such switches with the respective resistors 32 1 , 32 2 , 32 3 and 32 4 and the input terminals of inverters 33 1 , 33 2 , 33 3 and 33 4 . When any of the switches 31FU, 31FD, 31CU and 31CD are closed, a logic signal at the low logic level "0" is applied to the input terminals of the respective inverters 33 1 , 33 2 , 33 3 and 33 4 . The "1" or "0" logic controlled by the switches 31FU, 31FD, 31CU and 31DC are inverted by the corresponding inverters to first input terminals of NAND circuits 34 1 , 34 2 , 34 3 and 34 4 , respectively. The pulses A 14 having a period of 4.096 m. sec. are applied from the timing counter 20, as coarse tuning pulses, to second inputs of the NAND circuits 34 3 and 34 4 . The pulses A 14 are also applied to a frequency divider 35 to be divided, for example, by 64, to provide fine tuning pulses having a period of 262.144 m. sec., and such fine tuning pulses are applied to second inputs of the NAND circuits 34 1 and 34 2 . The "1" or "0" logic signals controlled by the switches 31FU, 31FD, 31CU and 31CD are also all applied to a AND circuit 36 which has its output terminal connected through an inverter 37 to NAND circuits 38 1 and 38 2 . Each of the NAND circuits 38 1 and 38 2 also has the fine tuning pulses from the frequency divider 35 applied to it. Further, the separate outputs E U and E D from the AFT circuit 120 are applied to inverters 39 1 and 39 2 , respectively, which have their outputs applied to the NAND circuits 38 1 and 38 2 , respectively. The outputs of the NAND circuits 34 1 and 38 1 are applied to a NAND circuit 301, while the outputs of the NAND circuits 34 2 and 38 2 are similarly applied to a NAND circuit 302. The output of the NAND circuit 301 is applied through an inverter 303 to a NAND circuit 304 which also receives the output of NAND circuit 34 3 directly. The output of the NAND circuit 302 is similarly applied through an inverter 305 to a NAND circuit 306 which also receives the output of the NAND circuit 34 4 . The outputs of the NAND circuits 304 and 306 are respectively applied to the NAND circuits 308 and 309, each of which also receives an AFT inhibit pulse P G from circuit 140, and the outputs of the NAND circuits 308 and 309 are applied as up-tuning pulses P U and down-tuning pulses P D , respectively, to the counter 40. Further, the outputs of the NAND circuits 308 and 309 are connected to an OR circuit 310 for providing pulses P UD to the memory rewriting circuit 130.

As shown schematically in FIG. 2, the counter 40 may be a conventional 14-bit up-down counter having 14 flip-flops 41 1 , 42 2 ---41 14 which have their states of conductivity changed sequentially to effect up or down counting in response to the pulses P U or P D , respectively, to establish, at the end of a counting interval, the respective bits of sequentially changing 14-bit channel identification codes B 1 , B 2 ---B 14 . In the programming mode of operation, the channel identification codes are applied from the counter 40 to the memory 50 for writing or storage of a selected one of such codes at a selectively activated address in the memory. Simultaneously, the sequentially changing channel identification codes are also applied from the counter 40 to the digital-to-analog converter 90 to provide a correspondingly varied control voltage for the varactor in a selected band of the electronic tuner 100. The flip-flops 41 1 ---41 14 of the counter 40 are further adapted, in the channel selecting mode of operation, to have their respective states established by the respective bits C 1 -C 14 of a memorized channel identification code which are read out of a selectively activated address in the memory 50 to the AND circuits 42 1 -42 14 which also receive a load pulse P B during the channel selecting operation for passing the bits read out of the memory, as hereinafter described in detail, and which have their outputs respectively connected to the flip-flops 41 1 -41 14 , respectively.

As shown schematically in FIG. 2, the counter 40 may be a conventional 14-bit up-down counter having 14 flip-flops 41 1 , 42 2 ---41 14 which have their states of conductivity changed sequentially to effect up or down counting in response to the pulses P U or P D , respectively, to establish, at the end of a counting interval, the respective bits of sequentially changing 14-bit channel identification codes B 1 , B 2 ---B 14 . In the programming mode of operation, the channel identification codes are applied from the counter 40 to the memory 50 for writing or storage of a selected one of such codes at a selectively activated address in the memory. Simultaneously, the sequentially changing channel identification codes are also applied from the counter 40 to the digital-to-analog converter 90 to provide a correspondingly varied control voltage for the varactor in a selected band of the electronic tuner 100. The flip-flops 41 1 ---41 14 of the counter 40 are further adapted, in the channel selecting mode of operation, to have their respective states established by the respective bits C 1 -C 14 of a memorized channel identification code which are read out of a selectively activated address in the memory 50 to the AND circuits 42 1 -42 14 which also receive a load pulse P B during the channel selecting operation for passing the bits read out of the memory, as hereinafter described in detail, and which have their outputs respectively connected to the flip-flops 41 1 -41 14 , respectively. As also shown in FIG. 2, the memory 50 may be made up of 16 memory units 51 1 , 51 2 ---51 16 at respective addresses in the memory 50, with the memory unit at each address being capable of storing 16 bits of digital information, that is, the 14 bits of a selected channel identification code from the counter 40 and 2-bits from an encoder 52 for the band indicating signal received from the circuit 80 for indicating whether the channel identified by the 14-bit digital code being stored at the respective address is a vhf or uhf channel, and, if it is a vhf channel, whether it is a low channel or a high channel in such broadcast band, respectively. Further, the memory 50 is schematically shown to include a decoder 53 which, in the programming and channel selecting modes of operation, receives the 2-bits of digital information representing the band of the channels identified by the 14-bit codes being applied to, or read out from, respectively, the memory units for providing a corresponding band identification signal applied to the electronic tuner 100 for selecting the corresponding band of the latter. Finally, the memory 50 also includes a decoder 54 which receives a 4-bit digital code from the address selecting circuit 70, as hereinafter described in detail. The 4-bit code is effective to activate or address the corresponding one of the memory units 51 1 , 51 2 ---51 16 . Preferably, the memory units of memory 50 are composed of non-volatile cells, such as, metal-nitride-oxide-silicon (MNOS) elements, so that the contents thereof, while being electrically alterable, are held unchanged during periods when the memory 50 is disconnected from a source of power.